# URP1X-300 (YH-5301E)

# Power Distribution Board Specification

URP1X 300W DC-DC Switching Power Distribution Board 80Plus Silver compliant

[This Document describes the specification of a switching power supply complying to industrial standards, namely Server System Infrastructure (SSI) specification.]

# **TABLE OF CONTENTS**

| 1. REVISION I        | .OG                                                                                                          | 7  |

|----------------------|--------------------------------------------------------------------------------------------------------------|----|

| 2. GENERAL S         | COPE                                                                                                         | 9  |

| 2.1.                 | Mechanical Overview                                                                                          | g  |

| 2.1.1.               | DC Input Connector                                                                                           |    |

| 2.1.2.               | Handle Retention Mechanism                                                                                   |    |

| 2.2.                 | Buzzer Sound and Identification                                                                              | 11 |

| 2.3.                 | Enviornmental Requirements                                                                                   |    |

| 2.3.1.               | Temperature and Humidity Requirements                                                                        |    |

| 2.3.2.               | Altitude Requirements                                                                                        |    |

| 2.3.3.               | Vibration and shock Requirements                                                                             |    |

| 2.3.4.               | Airflow Requirements                                                                                         |    |

| 2.3.5.               | Acoustic Requirements                                                                                        |    |

| 3. ELECTRICA         | LL PERFORMANCE                                                                                               | 13 |

| 3.1.                 | Power Input Specification                                                                                    |    |

| 3.1.1.               | Power Bus and Signal Connector                                                                               |    |

| 3.1.2.               | Power Inlet connector                                                                                        |    |

| 3.1.3.               | Input voltage and frequency specification for the Power Module                                               | 14 |

| 3.1.4.               | Input current                                                                                                | 14 |

| 3.1.5.               | Line Fuse                                                                                                    | 14 |

| 3.1.6.               | Line inrush                                                                                                  |    |

| 3.1.7.               | Input Power Factor Correction (only AC input)                                                                |    |

| 3.1.8.               | Line dropout                                                                                                 |    |

| 3.1.9.               | Efficiency                                                                                                   |    |

| 3.1.10.              | Suspeceptibility Requirements                                                                                |    |

| 3.1.10.1.            | Electrical Discharge Susceptibility                                                                          |    |

| 3.1.10.2.            | Fast Transient/Burst                                                                                         |    |

| 3.1.10.3.            | Radiated Immunity                                                                                            |    |

| 3.1.10.4.            | Surge Immunity                                                                                               |    |

| 3.1.10.5.            | AC line Transient Specification                                                                              |    |

| 3.1.10.6.<br>3.1.11. | AC line fast transient (EFT) specification  Electromagnetic Compatibility Requirements for AC input supplies |    |

| 3.1.11.<br>3.1.12.   | Power Recovery                                                                                               |    |

| 3.1.12.              | Voltage Brown Out                                                                                            |    |

| 3.1.14.              | Line Leakage Current                                                                                         |    |

| 3.2.                 | DC output voltages                                                                                           | 18 |

| 3.2.1.               | Grounding                                                                                                    | 18 |

| 3.2.2.               | Output rating                                                                                                | 18 |

| 3.2.3.               | Remote Sense                                                                                                 | 19 |

| 3.2.4.               | Auxilary Output (Standby)                                                                                    | 19 |

| 3.2.5.               | No load operation                                                                                            |    |

| 3.2.6.               | Peak load operation                                                                                          |    |

| 3.2.7.               | Voltage Regulation                                                                                           |    |

| 3.2.8.               | Ripple and Noise Regulation                                                                                  |    |

| 3.2.9.               | Dynamic loading                                                                                              |    |

| 3.2.10.              | Capacitive load                                                                                              | 20 |

| 3.2.11.       | Maximum load change                                                                                   |    |

|---------------|-------------------------------------------------------------------------------------------------------|----|

| 3.2.12.       | Close loop stability                                                                                  |    |

| 3.2.13.       | Residual Voltage Immunity in Standby mode                                                             |    |

| 3.2.14.       | Common Mode Noise                                                                                     |    |

| 3.2.15.       | Soft starting                                                                                         |    |

| 3.2.16.       | Hot Swap Requirements                                                                                 |    |

| 3.2.17.       | Load sharing control                                                                                  | 21 |

| 3.3.          | Timing Requirements                                                                                   |    |

| 3.3.1.        | Output Voltage Timing                                                                                 |    |

| 3.3.2.        | Overshoot                                                                                             |    |

| 3.3.3.        | Undershoot                                                                                            |    |

| 3.3.4.        | Temperature coefficient                                                                               |    |

| 3.4.          | Control and Indicator functions                                                                       |    |

| 3.4.1.        | PSON# Input Signal (Power supply enable)                                                              |    |

| 3.4.2.        | PSKILL Input Signal                                                                                   |    |

| 3.4.3.        | Power OK (PG or PWOK) Output Signal                                                                   |    |

| 3.4.4.        | SMBAlert# (PSAlert) Output Signal Pin                                                                 |    |

| 3.4.4.1.      | Smart Ride-Through (SmaRT)                                                                            |    |

| 3.4.4.2.      | Thermal CLST                                                                                          |    |

| 3.4.5.        | Power Distribution Board Fail (B/P Fail) Input Signal Pin                                             | 27 |

| 4. Energy Sa  | aving Features                                                                                        | 27 |

| 4.1.          | greenRedundancy™ Operation                                                                            | 27 |

| 4.1.1.        | greenRedundancy™ and standard redundancy operation support                                            |    |

| 4.1.2.        | greenRedundancy™ Disabling                                                                            |    |

| 4.1.3.        | greenRedundancy™ Power Module Steady State                                                            |    |

| 4.1.4.        | greenRedundancy <sup>TM</sup> Power Module Start Up requirements                                      |    |

| 4.1.5.        | greenRedundancy™ Signal requirements                                                                  |    |

| 4.1.6.        | greenRedundancy <sup>TM</sup> Active Module rotation                                                  |    |

| 4.1.7.        | greenRedundancy™ control circuitry                                                                    |    |

| 5. Protection | on circuits                                                                                           | 29 |

| 5.1.          | Over Voltage Protection (OVP <sub>main</sub> & OVP <sub>auxilary AR</sub> )                           |    |

|               |                                                                                                       |    |

| 5.2.          | Over Current and Short Circuit Protection (OCP/SCP <sub>main</sub> & OCP/SCP <sub>auxilary AR</sub> ) |    |

| <i>5.3.</i>   | Over Temperature Protection (OTP <sub>AR</sub> )                                                      | 30 |

| 5.4.          | Fan Failure Protection <sub>AR</sub>                                                                  | 30 |

| 6. Power Su   | ipply Management                                                                                      | 31 |

| 6.1.          | Hardware Layer                                                                                        | 31 |

| 6.1.1.        | Capancitance for SMBus                                                                                |    |

| 6.1.2.        | I2c Bus noise requirement                                                                             |    |

| 6.1.3.        | Pull UpsPull Ups                                                                                      |    |

| 6.2.          | Power Supply Management Controller (PSMC)                                                             | 31 |

| 6.2.1.        | Related Documents                                                                                     |    |

| 6.2.2.        | Data Speed                                                                                            |    |

| 6.2.3.        | Bus Errors                                                                                            |    |

| 6.2.4.        | General Call Address                                                                                  |    |

| 6.2.5.        | Group Command                                                                                         |    |

| 6.2.6.        | Extended Command                                                                                      |    |

| 6.2.7.        | Write Protection (WP)                                                                                 |    |

| 6.2.8.             | Firmware Updates                             |    |

|--------------------|----------------------------------------------|----|

| 6.2.9.             | Sensor Accuracy                              |    |

| 6.2.10.            | PSMC Sensors                                 |    |

| 6.3.               | Power Supply Field Replacement Unit (FRU)    |    |

| 6.3.1.<br>6.3.2.   | FRU DataFRU Device protocol                  |    |

| 6.3.3.             | FRU Data Format                              |    |

| 7. ENVIRON         | IMENTAL                                      | 36 |

| 7.1.               | Temperature                                  | 36 |

| 7.2.               | Humidity                                     | 36 |

| <i>7.3.</i>        | Altitude                                     | 36 |

| 7.4.               | Vibration                                    | 36 |

| 7.5.               | Mechanical Shock                             | 37 |

| 7.6.               | Thermal shock (Shipping)                     | 37 |

| 7.7.               | Catastrophic Failure                         | 37 |

| 7.8.               | EMI                                          | 37 |

| 7.9.               | Magnetic Leakage Fields                      | 37 |

| 7.10.              | Voltage Fluctuations and Flicker             | 37 |

| 8. REGULAT         | ГОRY Requirements                            | 37 |

| 8.1.               | Product Safety Compliance                    | 37 |

| 8.2.               | Product EMC Compliance – Class B Compliance  | 38 |

| 8.3.<br>8.3.1.     | Maximum Leakage current to ground Hi-pot     |    |

| 8.4.               | Electrostatic Discharge (ESD)                | 38 |

| 8.5.               | Certifications / Registrations/ Declerations | 38 |

| 8.6.<br>8.6.1.     | Comonent Regulation Requirements             |    |

| 9. Reliabilit      | ty / Waranty / Service                       | 39 |

| 9.1.               | Component De-rating                          | 39 |

| 9.2.               | Component Life requirement                   | 39 |

| 9.3.               | Mean Time between Failures (MTBF)            | 40 |

| 9.4.               | Warranty                                     | 40 |

| 9.5.               | Serviceability                               | 40 |

| 10. MISCELL        | ANEOUS                                       | 40 |

| 10.1.              | Marking                                      |    |

| 10.1.1.<br>10.1.2. | Model labelFirmware ID Label (FW ID)         |    |

| 10.1.2.<br>10.2.   | Outline Dimensions                           |    |

| 10.4.              | Outilite Dillicitations                      | 41 |

| 10.2.1.        | Power Supply Card Edge Dimension              | 41 |

|----------------|-----------------------------------------------|----|

| 10.3.          | Packing                                       | 42 |

| 10.3.1.        | Single Packing                                |    |

| 10.3.1.1.      | Single Packing Label                          |    |

| 10.3.2.        | Multi Packing                                 |    |

| 10.3.2.1.      | Multi Packing Label                           |    |

| 10.3.3.        | Palletization                                 | 42 |

| 10.3.3.1.      | Pallet Label                                  | 42 |

| 11. PSMC Inter | face (PMBus - FW ID P20000)                   | 42 |

| 11.1.          | Data Formats                                  | 42 |

| 11.2.          | Power Sensors                                 | 42 |

| 11.2.1.        | VOUT_MODE                                     | 43 |

| 11.2.2.        | Sensor Averaging                              | 43 |

| 11.3.          | Thermal management                            | 43 |

| 11.4.          | Status commands                               | 44 |

| 11.5.          | Limit commands                                | 44 |

| 11.5.1.        | Default Limits for System Controllable Limits | 44 |

| 11.5.2.        | Manufacturer Controlled Limits                | 44 |

| 11.6.          | Faults and Error Correction                   | 44 |

| 11.7.          | Capability and inventory reporting            | 45 |

| 11.8.          | Write Protection                              | 45 |

| 11.9.          | Interrupts                                    | 45 |

| 11.10.         | Firmware unarade                              | 46 |

# **Basic Specification**

- DC to DC switching power distribution board

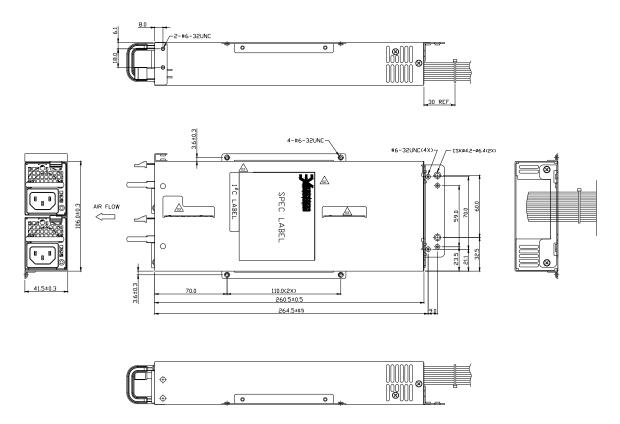

- Dimension: 41.5mm (height) x 106mm (width) x 260.5mm (length)

- 12V main input and 5Vsb auxiliary input

- Allows AC and DC input power module with the complying power bus

- Max. ouput of the PDB is 300W combined.

- Must meet class B EMI compliance in chassis

- Three main outputs +12V, 3.3V, 5V and one auxiliary output +5Vsb

- Traditional and green redundant support

- Hot-Swap function support for the pwer modules

- Passive cooled with PWM FAN of power modules

- Operation Temperature range: -5°C ~ 50°C @ full load

- Power Supply Management Controler (PSMC) for Smart Monitoring and control of the power supply

- EEPROM for FRU information

- i2c-Bus compliant communication bus (SDA, SCL) at 100kHz

- PS\_Alert# , PWOK#, Buzzer signaling

- Protections: OCP,OVP, OPP, UVP, OTP, SCP, FFP,

- Safety Compliance: BSMI, CB, CE, CCC, cUL, UL, TÜV

- Envirnmental Compliance: ROHS, WEEE, REACH

**PAGE: 6 OF 46**

# 2. GENERAL SCOPE

This specification describes the performance characteristic of a 300W AC-DC switching power distribution board (PDB) with a +12V main DC input and a +5Vsb auxiliary input. The PDB will switch into 3.3V and 5V main output and distribute 12V along with 5Vsb auxiliary. The PDB shall be able to operate with a single power supply module, or in a N+1 parallel hot-plug able operation with active load sharing in a N+1 redundant configuration. Mixed operation of different input type power modules (AC-DC) is allowed.

# 2.1. Mechanical Overview

The physical size of the PDB enclosure is intended to accommodate power supplies with a power range of up to 300watts. The physical size is 41.5mm x 106mm x 260.5mm (height x width x length).

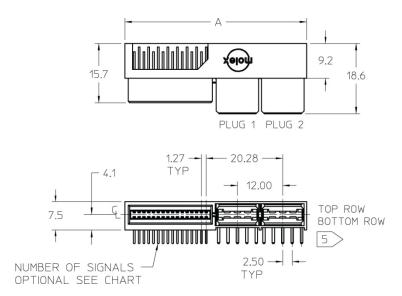

The power supply, which mates into this PDB, shall have a card edge for the DC outputs and signal pins, mating with Molex LPH series connector.

Input power plugs directly into the external face of the power supply module.

Figure 1 - PDB Dimension

# 2.1.1. DC Input Connector

The power supply shall have a card edge to mate with the Molex Low Profile Hybrid (LPH) Interconnect system. The Matting connector at PDB side is Molex PN 45984-4343.

**PAGE: 9 OF 46**

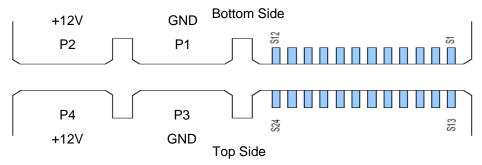

Figure 2 - Card Edge Pin Out Location

# Pin Assignment :

- P1~4,: Power Circuits

- S1 ~ S24: Signal Circuits

**Table 1 - Card Edge Pin Out Definition**

| Pin Name  | Signal Name       | Function                                        |

|-----------|-------------------|-------------------------------------------------|

| P1 Bottom | RTN GND           | +12V return                                     |

| P2 Bottom | Main_output       | +12V                                            |

| РЗ Тор    | RTN GND           | +12V return                                     |

| P4 Top    | Main_output       | +12V                                            |

| S1        | Main_output Sense | +12VS                                           |

| S2        | GND Sense         | +12V RTN Sense                                  |

| S3        | +MO IS            | +12V Main output Current share bus              |

| S4        | SMB_Alert TTL     | SMB_Alert for failure notification              |

| S5        | SDA               | I2c Data signal                                 |

| S6        | SCL               | I2c Clock signal                                |

| S7        | + PS_Kill         | In order to switch of the Main output (shorter) |

| S8        | PSON              | Power enable input                              |

| S9        | PWOK              | Pwr OK output                                   |

| S10       | A1                | I2c address bit 1                               |

| S11       | Stby_Output       | +5Vsb                                           |

| S12       | Stby_Output       | +5Vsb                                           |

| S13       | reserved          | reserved                                        |

| S14       | Present#          | Power supply present                            |

| S15       | A0                | I2c address bit 0                               |

| S16       | A2                | I2c address bit 2 (DGND, as 1+1 only)           |

| S17       | Vs                | Reserved for Factory use (+15Vcc)               |

| S18       | EEPROM_WP         | EEPROM write protection                         |

| S19       | Input_OK#         | Input present signal                            |

| S20       | grRD#             | Green Redundancy input                          |

| S21       | PDB-Fail          | PDB Fail                                        |

| S22       | Vs                | Reserved for factory use (NC)                   |

| S23       | Stby_Output       | +5Vsb                                           |

| S24       | Stby_Output       | +5Vsb                                           |

PAGE: 10 OF 46

Figure 3 - PDB Mating Connector

#### 2.1.2. Handle Retention Mechanism

The power supply module shall have a handle to assist extraction. The module shall be able to be inserted and extracted without the assistance of tools. The power supply shall have a retention mechanism, which retains the power supply into the PDB cage or enclosure during all mechanical shock (50G) and vibration testing. The handle shall protect the operator from any burn hazard through the use of Industrial designed plastic handle or equivalent approved material.

# 2.2. Buzzer Sound and Identification

The PDB shall have a Buzzer for indication of the power system status.

The buzzer is driven by an internal circuitry and should sound in a N+1 configuration even without AC power.

The Buzzer function can be switched off by hardware or i2c command.

Connector for disabling Buzzer is: TDB I2C command for disabling Buzzer is: TDB

The BUZZER TYPE: TDB or equal.

**Table 2 - Buzzer Status Information**

| Power system condition            | PDB Buzzer     |

|-----------------------------------|----------------|

| No AC power to all PSU            | OFF            |

| No AC power to one PSU only       | 0.5Hz buzzing  |

| AC present/only standby output on | OFF            |

| Power supply DC output ON and OK  | OFF            |

| One power module failure          | 1Hz buzzing    |

| PDB fail                          | Steady buzzing |

# 2.3. Enviornmental Requirements

The PDB shall operate within all specified limits over specified conditions in 2.3. The defined operation condition include temperature, humidity, altitude, shock and vibration.

PAGE: 11 OF 46

#### 2.3.1. Temperature and Humidity Requirements

The PDB shall operate within all specified limits over  $T_{op}$  temperature range and specified humidity Range. All airflow shall pass through the PDB and not over the exterior surfaces of the PDB cage.

The power supply shall withstand thermal storage specified in T<sub>non-OP</sub> without any damage.

Table 3 - Temperature Requirements

| Item                 | Description                                  | MIN | MAX | Unit   |

|----------------------|----------------------------------------------|-----|-----|--------|

| T <sub>OP</sub>      | Operating temperature range.                 | -5  | 50  | °C     |

| ΔΤ                   | Max temperature rise across power supply     |     | 15  | °C     |

| T <sub>non-OP</sub>  | Non-Operating temperature range.             | -40 | 70  | °C     |

| $T_{\Delta\_change}$ | Rate of temperature change.                  |     | 10  | °C/hrs |

| Hop                  | Operating humidity range, non condensing     |     | 85  | %      |

| H <sub>non-OP</sub>  | Non-Operating humidity range, non condensing |     | 95  | %      |

# 2.3.2. Altitude Requirements

The PDB shall operate within all specified limits over  $A_{op}$  Altitude range. The change pressure condition shall not harm the PDB and the operation within specified regulations shall be assured.

The PDB shall withstand Altitude storage specified in A<sub>non-OP</sub> without any damage.

Table 4 - Altitude Requirements

| Item                | Description                   | MIN | MAX   | Unit |

|---------------------|-------------------------------|-----|-------|------|

| $A_{OP}$            | Operating Altitude range.     | 0   | 5000  | m    |

| A <sub>non-OP</sub> | Non-Operating Altitude range. | 0   | 15000 | m    |

# 2.3.3. Vibration and shock Requirements

The PDB shall operate within all specified limits over Gop Shock Vibration range.

The PDB shall withstand Shock Vibration storage specified in Gnon-OP without any damage.

Table 5 - Shock Vibration Requirements

| Item                | Description                          | MIN       | MAX       | Unit               |

|---------------------|--------------------------------------|-----------|-----------|--------------------|

| $G_{OP}$            | Operating Shock Vibration range.     | 0.01@10Hz | 0.02@20Hz | G <sup>2</sup> /Hz |

| $G_{\text{non-OP}}$ | Non-Operating Shock Vibration range. | 0.02@20Hz | 0.02@1kHz | G <sup>2</sup> /Hz |

| $S_{OP}$            | Acceleration Shock while operation.  |           | 10        | G                  |

| S <sub>non-OP</sub> | Acceleration Shock non-operation     |           | 50        | G                  |

# 2.3.4. Airflow Requirements

The PDB shall be passively cooled through the air flow provided by the power module. The airflow direction shall be in either direction (inside out, pulling or outside in, pushing).

The airflow shall be increased according to specification in Table 6. The conditions must be satisfied under the maximum inlet temperature and altitude limits as specified in the table.

All airflow shall pass through the PDB and not over the exterior surfaces of the power subsystem.

PAGE: 12 OF 46

Table 6 - Airflow and Thermal Requirements

| Operation<br>Condition | Load (W)                                  | Minimum<br>Requirement<br>Airflow (CFM) | Maximum<br>System<br>Temp. (°C) | Maximum<br>Inlet Temp.<br>(°C) | Altitude |

|------------------------|-------------------------------------------|-----------------------------------------|---------------------------------|--------------------------------|----------|

| 1                      | Acoustic- Idle<br>120W (40%)              | TBD                                     | 25                              | 45                             | 900      |

| 2                      | Acoustic - Operating 180W (60%)           | TBD                                     | 25                              | 45                             | 900      |

| 3                      | Performance – Max T<br>300W (100%)        | TBD                                     | 35                              | 50                             | 900      |

| 4                      | Performance – Max Altitude<br>300W (100%) | TBD                                     | 28                              | 43                             | 5000     |

Figure 4 - PS Impedance Requirement

TBD

# 2.3.5. Acoustic Requirements

The PDB airflow shall be provided by the system or power module side. The Fan's installed into the power module shall not exceed the below requirements noise requirements.

**Table 7 - Acoustic Requirements**

| Operating<br>Condition | Volumetric<br>Flow,<br>stand alone<br>(CFM) | Inlet Temperature<br>Condition (°C) | % of Maximum Loading<br>Condition | Acoustic Noise(dB)<br>(Ref.) |

|------------------------|---------------------------------------------|-------------------------------------|-----------------------------------|------------------------------|

| Idle                   | TBD                                         | 25                                  | 40                                | 40                           |

| Operating              | TBD                                         | 25                                  | 60                                | 56                           |

| Maximum                | TBD                                         | 25                                  | 100                               | 66                           |

### 3. ELECTRICAL PERFORMANCE

# 3.1. Power Input Specification

# 3.1.1. Power Bus and Signal Connector

The PDB shall have a common Power Bus and signal connector complying to Molex LPH interconnect series. The exact PN for the interconnect is Molex PN 45984-4343.

The Pin definition shall comply with chapter 2.1 and shall provide 12VDC as main input and 5VsbDC as auxiliary input.

# 3.1.2. Power Inlet connector

The PDB has no direct power AC inlet connector. The power inlet shall be found at the power module. Dependant on the input power version, it shall comply to below requirements:

1. AC Version : Comply with IEC 320 C-14 power inlet connector specification. This inlet shall be rated for operation at 15A/250VAC.

PAGE: 13 OF 46

#### 3.1.3. Input voltage and frequency specification for the Power Module

The power modules inserted into the PDB shall operate within all specified limits over the following input range. The power supply shall power off if the AC or DC input is below  $V_{low\_limit}$  and shall start (auto recover) if  $V_{recover}$  is reached. Input of voltages below  $V_{recover}$  shall not cause any damage to the power supply module nor the PDB, including the input fuse.

The PDB shall supply the full output power, as long the power supply module is operating within specifications.

Table 8 - Rated output power for each input voltage range

| Parameter | Minimum input   | Rated Input             | Maximum input | VACrecover  | VAC <sub>low_limit</sub> |

|-----------|-----------------|-------------------------|---------------|-------------|--------------------------|

| 115 VAC   | $90V_{\rm rms}$ | $100\text{-}127V_{rms}$ | $132V_{rms}$  | 85VAC ±5VAC | 75VAC ±5VAC              |

| 230 VAC   | $180V_{rms}$    | $200\text{-}240V_{rms}$ | $264 V_{rms}$ |             |                          |

| Frequency | 47Hz            | 50/60Hz                 | 63Hz          |             |                          |

# 3.1.4. Input current

The maximum input current defines the maximum possible output current, to ensure the proper function of the PDB to meet all defined specifications.

Table 9 - Maximum input current

| Input voltage | Input current | Inrush current | Max power | Peak power |

|---------------|---------------|----------------|-----------|------------|

| 90-132VAC     | 5A*           | 40A*           | 300W      | 400W       |

| 180-264VAC    | 3A*           | 60A*           | 300W      | 400W       |

<sup>\*:</sup>single power supply module

#### **3.1.5.** Line Fuse

The power supply module inserted to the PDB shall incorporate one input fuse on the line side for input over-current protection to prevent damage to the power supply and PDB, to meet product safety requirements. Fuses should be slow blow type or equivalent to prevent nuisance trips. AC inrush current shall not cause the AC line fuse to blow under any conditions. All protection circuits in the power supply shall not cause the AC fuse to blow unless a component in the power supply has failed. This includes DC output load short conditions.

# 3.1.6. Line inrush

The power supply module must meet inrush requirements for any rated AC voltage, during turn on at any phase of AC voltage, during a single cycle AC dropout condition, during repetitive ON/OFF cycling of AC, and over the specified temperature range ( $T_{OP}$ ). The peak Inrush current shall be less than the ratings of its critical components (including input fuse, bulk rectifiers, and surge limiting device).

The maximum AC line inrush current for this power module is defined in the complying specification and is dependent on power module utilized.

Inrush current shall be measured at an ambient temperature of 25 deg C after the input voltage has been removed from the power supply for a minimum of 10 minutes.

# 3.1.7. Input Power Factor Correction (only AC input)

The input Power Factor shall be greater than 0.90/115Vac and 0.90/230Vac (show the below actual PF curve)over all input voltages at loads greater than 100% of the power supply's rated output, and meet Energy start 4.0 level .

PAGE: 14 OF 46

**Table 10 - Power Factor Correction**

| Input voltage | 20% loading | 50% loading | 100% loading |

|---------------|-------------|-------------|--------------|

| 115VAC        | 0.70        | 0.80        | 0.90         |

| 230VAC        | 0.70        | 0.80        | 0.90         |

# 3.1.8. Line dropout

An Line dropout is a transient condition defined as the Input to the power supply module drops to 0 VAC at any phase of the AC line for any length of time. During an AC dropout the power supply and PDB must meet dynamic voltage regulations requirements. An AC line dropout of any duration shall not cause dripping of the control signals and protection circuits. If the AC dropout lasts longer than the holdup time, the power supply system should recover when VAC meets VC<sub>recover</sub> and meet all turn on requirements. A Input dropout of any length shall not cause any damage to the power supply system.

Table 11 - Holdup time until Power output goes out of regulations

| Loading | Main output | Standby output |

|---------|-------------|----------------|

| 50%     | 24mS        |                |

| 80%     | 20mS        |                |

| 100%    | 16mS        | 70mS           |

# 3.1.9. Efficiency

The minimum efficiency of the power system measured at an input voltage of 115V or 230V and the maximum load shall be 80%.

# 3.1.10. Suspeceptibility Requirements

The power supply system with the PDB shall meet the following electrical immunity requirements when connected to a cage with an external EMI filter, which meets the criteria defined in the SSI document EPS Power Supply Specification.

Table 12 - Performance criteria

| Level | Description                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| A     | The apparatus shall continue to operate as intended. No degradation of performance.                                                  |

| I D   | The apparatus shall continue to operate as intended. No degradation of performance beyond spec. limits.                              |

| С     | Temporary loss of function is allowed provided the function is self-recoverable or can be restored by the operation of the controls. |

# 3.1.10.1. Electrical Discharge Susceptibility

The power supply shall comply with the limits defined in EN 55024:1998 using the IEC 61000-4-2:1995 test standard and performance criteria B defined in Annex B of CISPR 24.

#### 3.1.10.2. Fast Transient/Burst

The power supply shall comply with the limits defined in EN55024:1998 using the IEC 61000-4-4:1995 test standard and performance criteria B define in Annex B of CISPR 24.

PAGE: 15 OF 46

#### 3.1.10.3. Radiated Immunity

The power supply shall comply with the limits defined in EN55024:1998 using the IEC61000-4-3:1995 test standard and performance criteria A defined in Annex B of CISPR 24.

# 3.1.10.4. Surge Immunity

The power supply shall be tested with the system for immunity to AC Ringwave and AC Unidirectional wave, both up to 2kV, per EN55024:1998, EN 61000-4-5:1995 and ANSI C62.45:1992.

The pass criteria include: No unsafe operation is allowed under any condition; all power supply output voltage levels to stay within proper spec levels; No change in operating state or loss of data during and after the test profile; No component damage under any condition.

The power supply shall comply with the limits defined in EN55024:1998 using the IEC 61000-4-5:1995 test standard and performance criteria B defined in Annex B f CISPR 24.

# 3.1.10.5. AC Line Transient Specification

AC line transient conditions shall be defined as "sag" and "surge" conditions.

"Sag" conditions are also commonly referred to as "brownout", these conditions will be defined as the AC line voltage dropping below nominal voltage conditions.

"Surge" will be defined to refer to conditions when the AC line voltage rises above nominal voltage. The power supply shall meet the requirements under the following AC line sag and surge conditions.

| Duration Sag Operating AC voltage Line frequency Performance criteria |      |                                 |                |                                                                 |  |

|-----------------------------------------------------------------------|------|---------------------------------|----------------|-----------------------------------------------------------------|--|

| Duration                                                              | Sag  | Operating AC voltage            | Line frequency |                                                                 |  |

| Continuous                                                            | 10%  | Nominal AC voltage              | 50/60Hz        | No loss of function or performance                              |  |

| 0 to AC cycle                                                         | 100% | Nominal AC voltage              | 50/60Hz        | Loss of function or performance is acceptable, self recoverable |  |

| >1 AC cycles                                                          | >10% | Nominal AC voltage              | 50/60Hz        | Loss of function acceptable, self recoverable                   |  |

| 0 to 1/2 AC<br>cycle                                                  | 30%  | Mid-point of nominal AC voltage | 50/60Hz        | No loss of function or performance                              |  |

**Table 13 - AC Line SAG transient performance.**

Table 14 - AC Line SURGE transient performance.

| AC Line Surge        |        |                                 |                |                                    |

|----------------------|--------|---------------------------------|----------------|------------------------------------|

| Duration             | Surge  | Operating ac voltage            | Line frequency | Performance criteria               |

| Continuous           | 10%    | Nominal AC voltage              | 50/60Hz        | No loss of function or performance |

| 0 to 1/2 AC<br>cycle | 1.301% | mid-point of nominal AC voltage | 50/60Hz        | No loss of function or performance |

# 3.1.10.6. AC line fast transient (EFT) specification

The power supply shall meet the EN61000-4-5 directive and any additional requirements in IEC1000-4-5:1995 and the level 3 requirements for surge-withstand capability, with the following conditions and exceptions:

- These input transients must not cause any out-of-regulation conditions, such as overshoot and undershoot, nor must it cause any nuisance trips of any of the power supply protection circuits.

- The surge-withstand test must not produce damage to the power supply.

The supply must meet surge-withstand test conditions under maximum and minimum DC-output load conditions.

PAGE: 16 OF 46

# 3.1.11. Electromagnetic Compatibility Requirements for AC input supplies

| Category                                         | Standard                                                                                      | Frequency                                                              | Level / Limits                                           | Performance<br>Criteria <sub>1</sub> |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------|--|

|                                                  | EN 55022                                                                                      | 30M -1GHz                                                              | Class B                                                  | _                                    |  |

|                                                  | CFR 47, Part<br>15, Subpart B                                                                 | 30M-1GHz<br>>1GHz (see<br>standard)                                    | Class B                                                  | _                                    |  |

| Radiated<br>Emissions                            | Additional requirements for DT   1.0 - 10.7GHz   1.24 - 1.3GHz   1.7 - 1.92GHz   10.7 - 18GHz |                                                                        | 70dBuV/m Pk<br>50dBuV/m Pk<br>50dBuV/m Pk<br>85dBuV/m Pk | 3dB Margin                           |  |

|                                                  | GR 1089, Issue<br>4                                                                           | 10k-10GHz,<br>E-Field and H-Field                                      | Section 3.2.1                                            |                                      |  |

|                                                  | EN 55022                                                                                      | 150k-30MHz                                                             | Class B                                                  |                                      |  |

| Conducted<br>Emissions                           | GR 1089, Issue<br>4, Section                                                                  | 150k-30MHz                                                             | Voltage, Table 3-<br>3&4                                 | 3dB Margin                           |  |

|                                                  | 3.2.2                                                                                         | 10k-30MHz                                                              | Current, Table 3-5                                       |                                      |  |

| AT&T NEDS (Network Equipment Development Stands) | ATT 801-900-<br>160 (Dec<br>2003)                                                             |                                                                        | See standard                                             |                                      |  |

| Stanusj                                          | EN 61000-4-3                                                                                  | 80M-2GHz                                                               | 10 V/meter                                               | A                                    |  |

|                                                  |                                                                                               | 806 - 960 MHz<br>1700 - 2025 MHz<br>2100 - 2200 MHz<br>2500 - 2690 MHz | 20 V/meter                                               | A                                    |  |

|                                                  | Additional                                                                                    |                                                                        | 50 V/meter                                               | A                                    |  |

| Radiated                                         | requirements                                                                                  | 880 - 915 MHz<br>1710 - 1785 MHz                                       | 35 V/meter                                               | A                                    |  |

| Immunity                                         | for BT and DT.                                                                                | 1920 - 1980 MHz                                                        | 50 V/meter                                               | A                                    |  |

|                                                  |                                                                                               | 2400 - 2483 MHz<br>5150 - 5350 MHz<br>5725 - 5820 MHz                  | 12 V/meter                                               | A                                    |  |

|                                                  | GR 1089, Issue<br>4                                                                           |                                                                        | 8.5 V/meter<br>Section 3.3.1                             | A                                    |  |

| ESD                                              | EN 61000-4-2                                                                                  |                                                                        | 8 KV contact,<br>15KV Air                                | В                                    |  |

| Electrical Fast<br>Transient                     | EN                                                                                            | 61000-4-4                                                              | +/- 2 KV                                                 | В                                    |  |

| Conducted                                        | EN 61000-4-6                                                                                  | 150 KHz - 80 MHz                                                       | 10Vrms                                                   | A                                    |  |

| Susceptibility                                   | GR 1089, Issue<br>4                                                                           | 10 KHz - 30 MHz                                                        | Section 3.3.2<br>Table 3-11                              | A                                    |  |

| Voltage Dips and                                 |                                                                                               | >95% reduction for                                                     | 10mS                                                     | В                                    |  |

| Sags 2                                           | EN 61000-4-11                                                                                 | >30% reduction for                                                     | 500mS                                                    | С                                    |  |

| 54 <b>5</b> 5 2                                  |                                                                                               | >95% reduction for                                                     | 500mS                                                    | С                                    |  |

# 3.1.12. Power Recovery

The PDB shall recover automatically (auto recover) after an input power failure. Input power failure is defined to be any loss of Input power that exceeds the dropout criteria.

PAGE: 17 OF 46

#### 3.1.13. **Voltage Brown Out**

The power supply shall comply with the limits defined in EN55024:1998 using the IEC 61000-4-11:1995 test standard and performance criteria C defined in Annex B of CISPR 24.

In addition the power supply shall meet the following requirements:

A continuous input voltage below the nominal input range shall not damage the power supply or cause overstress to any power supply component. The power supply must be able to return to normal power up state after a brownout (Sag) condition. During brownout test of defined input range @ 300W with 3mins ramp, input current shall never exceed fuse and shall not blow the fuse.

#### 3.1.14. **Line Leakage Current**

The maximum leakage current to ground for each power supply shall be 3.5mA when tested at 240VAC.

#### 3.2. DC output voltages

#### 3.2.1. Grounding

The output ground of the pins of the power supply provides the output power return path. The ground output at the PDB shall be connected to the safety ground (power supply enclosure) and PCB card edge. This grounding should be well designed to ensure passing the max allowed Common Mode Noise levels.

The power supply system shall be provided with a reliable protective earth ground. All secondary circuits and D2D shall be connected to protective earth ground. Resistance of the ground returns to chassis shall not exceed  $1.0 \text{m}\Omega$ . This path may be used to carry DC-current.

#### 3.2.2. **Output rating**

The following table defines the power and current rating of the 300W PDB. The combined output power of all outputs shall not exceed the rated output power. The power supply system must meet both static and dynamic voltage regulation requirements.

The utilized power module defines the maximum output power of the PDB. In a mixed operation, the power module with the lower output power shall define the maximum output limit in order to achieve safe redundant operation. In case the max output limit in a 1+0 had been exceeded, the power module shall latch OCP or OPP event. In a 1+1 operation, the current will be shared and redundancy function will be changed to forced current share mode, if the max. output rating of the lower power module had been exceeded.

Table 15 - Output Power and Current Ratings

The maximum combined steady output power shall be 300W, no matter how the current draw will be combined.

| O LIMBLIM | NOM               | OUTI | PUT CURF | RENT |       | CONDIMION     |

|-----------|-------------------|------|----------|------|-------|---------------|

| OUTPUT    | VOLT              | MIN  | MAX      | Peak | UNITS | CONDITION     |

| 1         | +3.3V             | 0    | 20 #a    | 24   | A     | combined #a & |

| 2         | +5V               | 0    | 20 #b    | 24   | Α     | #b            |

|           |                   |      |          |      |       | power≦140W    |

| 3         | +12V              | 0    | 24       | 31.7 | A     |               |

| 4         | -12V              | 0    | 0.5      | N/A  | A     |               |

| 5         | +5V <sub>sb</sub> | 0    | 3        | 4    | A     |               |

PAGE: 18 OF 46

#### 3.2.3. Remote Sense

The PDB shall have remote sense for the +3.3V (3.3VS) and return (ReturnS) if the server signal connector (i2c connector) is implemented. The remote sense return (ReturnS) is used to regulate out ground drops for all output voltages; +3.3V, +5V,  $+12V_{1,2,3,4}$ , -12V, and +5Vsb. The 3.3V remote sense (3.3VS) is used to regulate out drops in the system for the +3.3V output. The remote sense input impedance to the PDB must be greater than 200W on 3.3.VS and ReturnS. This is the value of the resistor connecting the remote sense to the output voltage internal to the PDB. Remote sense shall be able to regulate out a minimum of 200mV drop on the +3.3V output. The remote sense return (ReturnS) shall be able to regulate out a minimum of 200mV drop in the power ground return. The current in any remote sense line shall be less than 5mA to prevent voltage sensing errors. The PDB shall operate within specification over the full range of voltage drops from the PDB's output connector to the remote sense points.

# 3.2.4. Auxilary Output (Standby)

The 5Vsb output shall be present when an input voltage greater than  $V_{recover}$  is applied to the power module.

# 3.2.5. No load operation

The power supply system shall meet all requirements except for the transient loading requirements when operated at no load on all outputs.

# 3.2.6. Peak load operation

The power supply shall be capable to hold the peak loading requirements for at least 15mS without going out of regulation or shutting down. Each output slew rate 0.05A/uS ,5Vsb minimum 0.3A.

# 3.2.7. Voltage Regulation

The power supply shall meet the Voltage regulation when operating at steady state condition, dynamic, peak load, Hot swap conditions must be meet +/-5%. These limits include the peak-peak ripple/noise.

The regulation of Table 16 shall be measured at the output connector of the power supply, subject to the dynamic loading conditions in paragraph 3.2.7.

|                         |         | Output voltage limits $(V_{dc})$ |         |           |           |  |

|-------------------------|---------|----------------------------------|---------|-----------|-----------|--|

| Output                  | Minimum | Nominal                          | Maximum | Unit      | Tolerance |  |

| +3.3V                   | +3.135  | +3.3                             | 3.47    | $V_{rms}$ | +5/-5%    |  |

| +5V                     | 4.75    | +5.0                             | 5.25    | $V_{rms}$ | +5/-5%    |  |

| +12V <sub>1,2,3,4</sub> | +11.64  | +12.0                            | +12.60  | $V_{rms}$ | +5/-3%    |  |

| -12V                    | -11.40  | -12.0                            | -13.08  | $V_{rms}$ | +9/-5%    |  |

| +5Vsb                   | 4.75    | 5                                | 5.25    | $V_{rms}$ | +5/-5%    |  |

Table 16 - Output Voltage regulation

#### 3.2.8. Ripple and Noise Regulation

Ripple and Noise is defined in table 17. Ripple and Noise shall be measured over a Bandwidth of 0Hz to 20MHz at the power supply output connector. A  $0.1\mu F$  ceramic capacitor and  $47\mu F$  of tantalum capacitor shall be placed at each point of measurement. The measurement points shall be as close as possible to the point of load. The ripple and noise specification shall be met over all load ranges and any line voltages with 1+N power supplies in parallel operation.

PAGE: 19 OF 46

Table 17- Ripple and Noise Regulation

| Output               | +3.3V   | +5V     | +12V     | -12V     | 5VSB    |

|----------------------|---------|---------|----------|----------|---------|

| Maximum ripple/noise | 50mVp-p | 50mVp-p | 120mVp-p | 120mVp-p | 50mVp-p |

# 3.2.9. Dynamic loading

The power supply shall operate within specified limits and meet regulation requirements for step loading and capacitive loading specified below.

The load transient repetition rate shall be tested between 50Hz to 5kHz at duty cycles ranging from 10%-90%. The load transient repetition rate is only a test specification. The  $\Delta$  step load may occur anywhere within the MIN load and the MAX load.

This shall be tested with no additional bulk capacitance added to the load.

**Table 18 - Transient Load Requirements**

| Output | Δ Step size      | Slew Rate  | Capacitive Load |

|--------|------------------|------------|-----------------|

| +3.3V  | 30% of max. load | 0.5A/ μsec | 1000μF          |

| +5V    | 30% of max. load | 0.5A/ μsec | 1000μF          |

| +12V   | 65% of max. load | 0.5A/ μsec | 2200μF          |

| +5VSB  | 25% of max. load | 0.5A/ μsec | 1μF             |

# 3.2.10. Capacitive load

The power supply shall operate within specifications over the capacitive loading ranges defined below in table 19

**Table 19 - Capacitive Loading Conditions**

| Output | Min  | Max      |

|--------|------|----------|

| +3.3V  | 10μF | 12,000μF |

| +5V    | 10μF | 12,000μF |

| +12V   | 10μF | 11,000μF |

| -12V   | 1μF  | 350μF    |

| +5VSB  | 1μF  | 350µF    |

# 3.2.11. Maximum load change

The power supply shall continue to operate normally when there is a step change  $\leq 1$  A/ $\mu$ sec. between minimum load and maximum load.

#### 3.2.12. Close loop stability

The power supply shall be unconditionally stable under all line/load/transient load conditions including capacitive load ranges. A minimum of: 45 degrees phase margin and -12dB gain margin is required. Closed-loop stability must be ensured at the maximum and minimum loads as applicable.

**PAGE: 20 OF 46**

#### 3.2.13. Residual Voltage Immunity in Standby mode

The power supply should be immune to any residual voltage placed on its outputs (typically a leakage voltage through the system from standby output) up to 500mV. There shall be no additional heat generated nor stressing of any internal components with this voltage applied to any individual or all outputs simultaneously. It also should not trip the protection circuits during turn on/off. The residual voltage at the power supply outputs for no load condition shall not exceed 100mV when Input voltage is applied.

#### 3.2.14. Common Mode Noise

The Common Mode noise on any output shall not exceed 350mV pk-pk over the frequency band of 10Hz to 200MHz. Measurement shall be made across a  $100\Omega$  resistor across the DC outputs, including ground at the DC output connector and chassis ground (power sub system enclosure),

#### 3.2.15. Soft starting

The power supply shall contain control circuit which provides monotonic soft start for its outputs without overstress of the Input line or any power supply components at any specified Input line or load condition.

#### 3.2.16. Hot Swap Requirements

Hot Swapping a power supply is the process of inserting and extracting a power supply from an operating power system. During this process the output voltages shall remain within the limits with the capacitive load specified. The hot swap test must be conducted when the system is operating under static, dynamic and zero loading conditions. The power supply can be hot swapped by the following method:

**Extraction:** The power supply may be removed from the system while operating with PSON# asserted, while in standby mode with PSON# de-asserted or with no AC applied. No connector damage should occur during unmating of the power supply from the power distribution board (PDB).

**Insertion:** The power supply may be inserted into the system with PSON# asserted, with PSON# de-asserted or with no AC power present for that supply. No connector damage should occur due to the mating of the output and input connector.

In general a failed (of by internal latch or external control) supply may be removed, then replaced with a good power supply, however, hot swap needs to work with operational as well as failed power supplies. The newly inserted power supply will get turned on into standby or Power On mode once inserted.

#### 3.2.17. Load sharing control

The +12 V output shall have active load sharing provided by inserted power modules. When operating at 50% of full load, the output current of any 1+1 power supplies shall be within (+/-10%). For example, if power supply #1 is operating at 12A, then all other power supplies within the system shall be operating between 10.8A to 13.2A (+/-10% of 12A).

All current sharing functions shall be implemented internal to the power supply module by making use of the 12VLS signal. The PDB (Housing Back Plane, for example YH-Part), shall connect the 12VLS signals between the power supplies together. The power supply shall be able to share with up to 1+N supply in parallel.

The failure of a power supply shall not affect the load sharing or output voltages of the other supplies still operating. The power supplies must be able to load share with 100mV of drop between different power supply's output.

If the load sharing is disabled by shorting the load share bus to ground, the power supply shall continue to operate within regulation limits for loads less than or equal to the rating of one power supply.

PAGE: 21 OF 46

Table 20 - Load share bus output characteristics

| Item                                            | Description                                                                                                                                                    | Min | Nominal               | Max | Units |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|-----|-------|

| V <sub>share</sub> ;<br>I <sub>out</sub> =Max.  | Voltage of load share bus at specified max output current                                                                                                      |     | 6                     |     | V     |

| $\Delta V_{\text{share}}/\Delta I_{\text{out}}$ | Slope of load share bus voltage with changing load                                                                                                             |     | 6/I <sub>outmax</sub> |     | V/A   |

| I <sub>share</sub> SINK                         | Amount of current the load share bus output from each power supply is allowed to sink                                                                          |     | 1.5                   |     | mA    |

| I <sub>share</sub> SOURCE                       | Amount of current the load share bus output from each power supply needs to source                                                                             |     | 1.5                   |     | mA    |

| T <sub>share</sub> ;<br>I <sub>out</sub> =Max.  | Delay from output voltages in regulation to load sharing active with maximum load of one power supply and two power supplies in parallel. (remote on/off only) |     |                       | 100 | msec  |

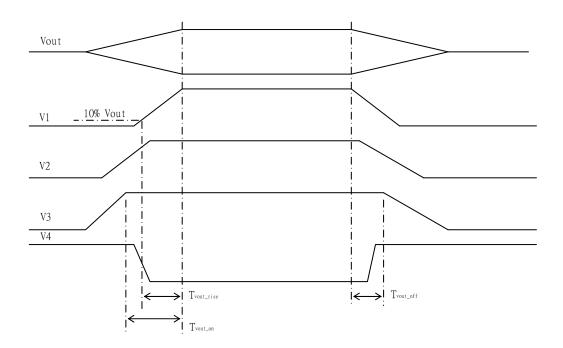

# 3.3. Timing Requirements

These are the timing requirements for the power supply operation. The output voltages must rise from 10% to within regulation limits ( $T_{vout\_rise}$ ) within 0.2 to 70ms. For 5Vsb, it is allowed to rise from 0.2 to 25ms. All main outputs shall rise positive monotonically and have a slop value between 0 V/mS to 0.1V/mS.

For 5Vsb output any 5ms segment of the 10% to 90% rise time waveform, a straight line draw between the end points of the waveform segment must have s slope  $\geq$  [Vout, nominal /20]V/mS.

Each output voltage shall reach regulation within 50mS ( $T_{vout\_on}$ ) of each other during turn on of the power supply system. Each output voltage shall fall out of regulation within 400mS ( $T_{vout\_off}$ ) of each other during turn off.

Table below shows the timing requirements for the power supply being turned on and off via the input power, with PSON held low and the PSON signal, with the input power applied.

# 3.3.1. Output Voltage Timing

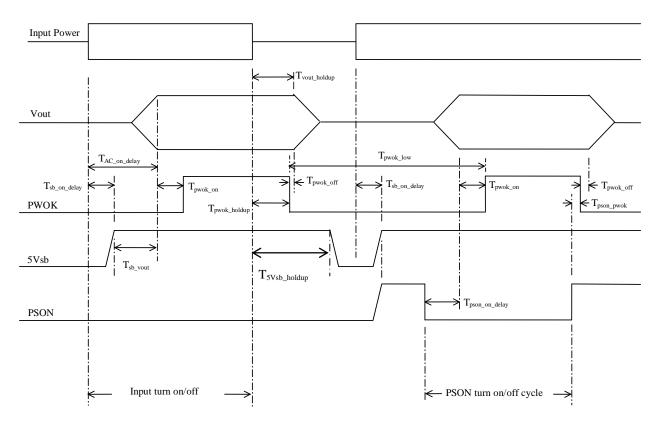

The timing of signals and outputs are specified in below Table 21 and illustrated in Figure 5 and Figure 6.

PAGE: 22 OF 46

Table 21 - Turn on/off timing

| Turn on                    | Description                                                                                         | Min | Max  | Units |

|----------------------------|-----------------------------------------------------------------------------------------------------|-----|------|-------|

| T <sub>vout rise</sub>     | Output voltage rise time for all main output                                                        |     | 70   | msec  |

|                            | Output voltage rise time for auxiliary output 5Vsb                                                  |     | 25   | msec  |

| T <sub>vout on</sub>       | All main outputs must be within regulation of each other within this time                           |     | 50   | msec  |

| $T_{vout off}$             | All main outputs must leave regulation within this time.                                            |     | 400  | msec  |

| T <sub>sb_on_delay</sub>   | Delay from AC being applied to 5VSB being within regulation                                         |     | 1500 | msec  |

| $T_{ac\_on\_delay}$        | Delay from AC being applied to all output voltage being within regulation                           |     | 2500 | msec  |

| $T_{vout\_holdup}$         | Time all main output 12VI voltages stay within regulation after loss of AC.                         | 16  |      | msec  |

| $T_{pwok\_holdup}$         | Delay from loss of AC to de-assertion of PWOK                                                       | 15  |      | msec  |

| T <sub>pson_on_delay</sub> | Delay from PSON# active to output voltages within regulation limits                                 | 5   | 400  | msec  |

| T <sub>pson_pwok</sub>     | Delay from PSON# deactivate to PWOK being de-asserted.                                              |     | 50   | msec  |

| T <sub>pwok_on</sub>       | Delay from output voltage(3.3V, 5V, 12V, -12V) within regulation limits to PWOK asserted at turn on | 100 | 500  | msec  |

| $T_{pwok\_off}$            | Delay from PWOK de-asserted to output voltages dropping out of regulation limits.                   | 1   |      | msec  |

| T <sub>pwok_low</sub>      | Duration of PWOK being in the de-asserted state during an off/on cycle using AC or the PSON signal  | 100 |      | msec  |

| T <sub>sb_vout</sub>       | Delay from 5Vsb being in regulation to main output being in regulation at AC turn on.               | 50  | 1000 | msec  |

| T <sub>5Vsb_holdup</sub>   | Time the 5Vsb output voltage stays within regulation after loss of AC                               | 70  |      | msec  |

Figure 5 - Output Voltage timing

Figure 6 - Turn On/Off Timing (Power Supply Signals)

# 3.3.2. Overshoot

Any output overshoot at turn on shall be less than 5% of the nominal output value. Any overshoot shall recover to within the specified regulation in less than 0.5mS

#### 3.3.3. Undershoot

Any output shall not undershoot at turn on or off cycle under any circumstances.

# 3.3.4. Temperature coefficient

After operating for 30 minutes or longer at 25° C ambient, the output voltages shall not change by more than  $\pm$  0.05 % per degree C for any given line and load conditions.

# 3.4. Control and Indicator functions

The following section define the input and output signals from the power supply. Signals that can be defined as low true use the following convention: Signal# = low true.

#### 3.4.1. PSON# Input Signal (Power supply enable)

The PSON# signal is required to remotely turn on/off the main output of the power supply.

PSON# is and active low signal that turns on the main output power rail. When this signal is not pulled low by the system or left open, the outputs (except the Standby output) turn off.

PSON# is pulled to a standby voltage by a pull-up resistor internal to the power supply. See Table 22.

PAGE: 24 OF 46

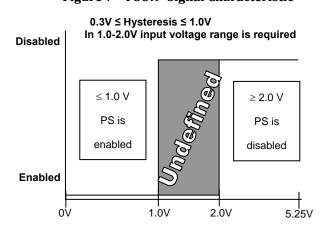

Accepts an open collector/drain input from the system. Signal Type Pul-up to Vsb located in the power supply. PSON# = Low ON PSON# = High or Open OFF PSON# = Low, PSKILL = Open OFF MIN MAX Logic level low (power supply ON) 0V 1.0V Logic level high (power supply OFF) 2.0V 5.25V  $\overline{\text{Source current}}$ ,  $V_{\text{pson}} = \text{low}$ 4mA Power up delay: Tpson on delay 400ms 5ms PWOK delay: Tpson pwol 50ms

Table 22 - PS ON# signal characteristics

Figure 7 - PSON# Signal Characteristic

# 3.4.2. PSKILL Input Signal

The purpose of the PSKILL pin is to allow for hot swapping of the power supply. The PSKILL pin on the power supply is shorter than the other signal pins. When a power supply is operating in parallel with other power supplies and then extracted from the system, the PSKill pin will quickly turn off the main output to prevent arcing of the DC output contacts.  $T_{PSKill}$  is the minimum time delay from the PSKill pin un-mating to when the power pins un-mate. The power supply must discharge its output inductor within this time from the un-mating of PSKill pin. When the PSKill signal pin is not pulled down or left open (power supply is extracting from the system or had not been inserted to the system), the power supply should shut down regardless of the condition of the PSON# signal.

The mating pin of this signal in the system shall be tied to ground. Internal to the power supply, the PSKILL pin shall be connected to a standby voltage through a pull-up resistor. Upon receiving a LOW state signal at the PSKILL pin, a PSON# signal shall enable the power supply to turn on.

See Table 23.

**Table 23 - PSKILL signal characteristics**

| Signal Type<br>(Input Signal to Supply) | Accepts a ground input from the system. Pull- up to Vsb located in the power supply. |       |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------|-------|--|--|

| PSKILL = Low, PSON# = Low               | ON                                                                                   |       |  |  |

| PSKILL = Low or Open, PSON# = Open      |                                                                                      | OFF   |  |  |

| PSKILL = Open , PSON# = Low             | OFF                                                                                  |       |  |  |

|                                         | MIN                                                                                  | MAX   |  |  |

| Logic level low                         | 0V                                                                                   | 0.4V  |  |  |

| (power supply ON)                       |                                                                                      |       |  |  |

| Logic level high                        | 2.4V                                                                                 | 5.25V |  |  |

PAGE: 25 OF 46

| (power supply OFF)                     |         |

|----------------------------------------|---------|

| Source current, $V_{pskill} = low$     | 4mA     |

| Delay from PSKILL=High to power supply | 100μsec |

| turned off (T <sub>PSKill</sub> )      |         |

# 3.4.3. Power OK (PG or PWOK) Output Signal

PWOK is a power good signal and shall be pulled HIGH by the power supply to indicate that all outputs are within regulation limits. When any output voltage falls below regulation limits, a internal failure or when AC power has been removed for a time sufficiently long, so that power supply operation is no longer guaranteed, PWOK will be de-asserted to a LOW state. The start of the PWOK delay time shall inhibited as long as any power supply output is in current limit.

See Table 24.

Table 24 - PWOK signal characteristics

| Signal Type                                           | Open collector/drain output from power supply. Pull-up to Vsb located in power supply. |         |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------------|---------|--|

| PWOK=High                                             | Power Good                                                                             |         |  |

| PWOK=Low                                              | Power Not Good                                                                         |         |  |

|                                                       | MIN                                                                                    | MAX     |  |

| Logic level low voltage, I <sub>sink</sub> =4mA       | 0V                                                                                     | 0.4V    |  |

| Logic level high voltage, I <sub>source</sub> = 200μA | 2.4V                                                                                   | 5.25V   |  |

| Sink current, PWOK=low                                |                                                                                        | 4mA     |  |

| Source current, PWOK=high                             |                                                                                        | 2mA     |  |

| PWOK delay: T <sub>pwok_on</sub>                      | 100ms                                                                                  | 500ms   |  |

| PWOK rise and fall time                               |                                                                                        | 100μsec |  |

| Power down delay: T <sub>pwok_off</sub>               | 1ms                                                                                    | 200ms   |  |

### 3.4.4. SMBAlert# (PSAlert) Output Signal Pin

This signal indicates that the power supply is experiencing a problem that the user should investigate. This shall be asserted due to Critical events or Warning events. The signal shall activate in the case of critical component temperature reached a warning threshold, general failure, over-current, over-voltage, under-voltage, failed fan. This signal may also indicate the power supply is reaching its end of life or is operating in an environment exceeding the specified limits.

#### 3.4.4.1. Smart Ride-Through (SmaRT)

SMBAlert# will also be asserted in case of a input power lost.

This function is part of the Smart ride-through (SmaRT) function in order to throttle the system and start up all put in greenRedundancy<sup>TM</sup> held power supplies.

The SMBAlert# needs to be asserted up on input power lost according to below table.

#### 3.4.4.2. Thermal CLST

SMBAlert\* shall also be utilized for warning of critical thermal component temperatures. The Thermal CLST shall assert when the component temperature, which shall be reported by a dedicated thermal probe, is reaching below specified  $\Delta T$  to critical shut down. The power supply shall report the temperature in addition to Thermal CLST through PMBus to the system, in order to increase fan speed to cool down environmental temperature.

This signal is to be asserted in parallel with LED turning solid red or blinking red/green. See Table 25.

PAGE: 26 OF 46

Table 25 - PSAlert# signal characteristics

| Signal Type                                     |                       | Open collector/drain output from power supply. Pull-up to Vsb located in power supply. |  |  |

|-------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------|--|--|

| Alert#=High                                     | Pov                   | Power OK                                                                               |  |  |

| Alert#=Low                                      | Power Alert to system |                                                                                        |  |  |

|                                                 | MIN                   | MAX                                                                                    |  |  |

| Logic level low voltage, I <sub>sink</sub> =4mA | 0V                    | 0.4V                                                                                   |  |  |

| Logic level high voltage, $I_{sink} = 50 \mu A$ | 2.4V                  | 3.46V                                                                                  |  |  |

| Sink current, Alert#=low                        |                       | 4mA                                                                                    |  |  |

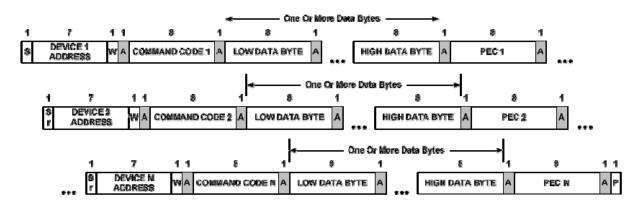

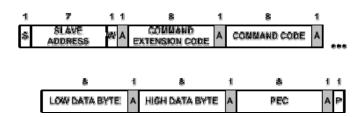

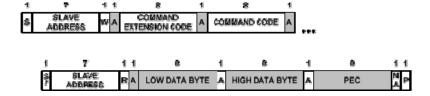

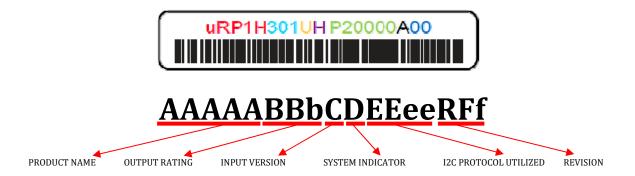

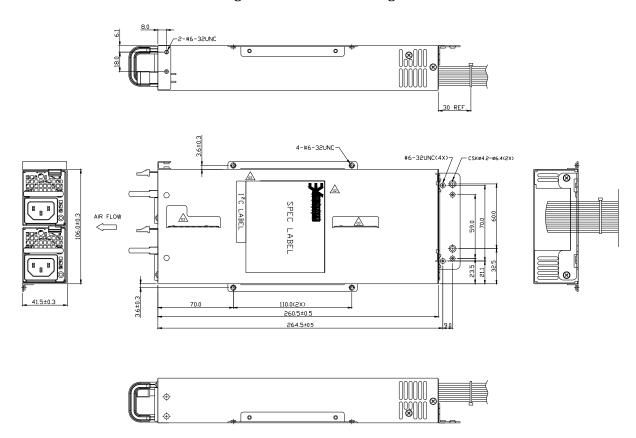

| Sink current, Alert#=high                       |                       | 50μΑ                                                                                   |  |  |