# LPDDR4X/LPDDR4 SDRAM

# RS4G32LV4D8BDT-53BT

#### **Features**

This data sheet is for LPDDR4X and LPDDR4 unified product based on LPDDR4X information. Refer to General LPDDR4 specification at the end of this data sheet.

- Ultra-low-voltage core and I/O power supplies

- $-V_{DD1} = 1.70-1.95V$ ; 1.80V nominal

- $-V_{DD2} = 1.06-1.17V$ ; 1.10V nominal

- $V_{DDQ}$  = 0.57–0.65V; 0.60V nominal or  $V_{DDO}$  = 1.06–1.17V; 1.10V nominal

- Frequency range

- 2133–10 MHz (data rate range per pin: 4266–20 Mb/s)

- 16n prefetch DDR architecture

- 8 internal banks per channel for concurrent operation

- Single-data-rate CMD/ADR entry

- Bidirectional/differential data strobe per byte lane

- Programmable READ and WRITE latencies (RL/WL)

- Programmable and on-the-fly burst lengths (BL = 16, 32)

- Directed per-bank refresh for concurrent bank operation and ease of command scheduling

- Up to 4.26 GB/s per die (x8)

- On-chip temperature sensor to control self refresh rate

- Partial-array self refresh (PASR)

- Selectable output drive strength (DS)

- Clock-stop capability

- · RoHS-compliant, "green" packaging

- Programmable V<sub>SS</sub> (ODT) termination

- Single-ended CK and DQS support

#### **Options**

- $V_{DD1}/V_{DD2}/V_{DDQ}$ : 1.80V/1.10V/0.60V or 1.10V

- Array configuration

- 4 Gig x 32 (2 channels x 16 I/O)

- Device configuration

- 4G08 x 8 die in package

- FBGA "green" package

- 200-ball TFBGA (10mm × 14.5mm, Ø0.28 SMD)

- Speed grade, cycle time

- 535ps @ RL = 32/36

- 468ps @ RL = 36/40

- Operating temperature range

- -25°C to +85°C

**Table 1: Key Timing Parameters**

| Speed | Clock Rate | Data Rate  | WRITE Latency Set A Set B |    | READ Latency |             |

|-------|------------|------------|---------------------------|----|--------------|-------------|

| Grade | (MHz)      | (Mb/s/pin) |                           |    | DBI Disabled | DBI Enabled |

| -53   | 1866       | 3733       | 16                        | 30 | 32           | 36          |

| -46   | 2133       | 4266       | 18                        | 34 | 36           | 40          |

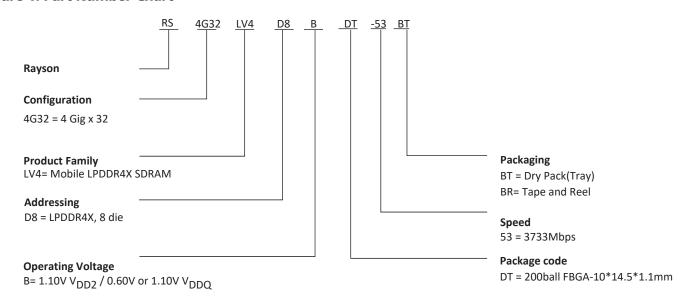

# **Part Number Ordering Information**

**Figure 1: Part Number Chart**

# **Important Notes and Warnings**

**Customer Responsibility.** Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or en-vironmental damages will result from failure of any semiconductor component.

**Limited Warranty.** In no event shall be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory.

# **Product Specification**

#### **General Description**

The 16Gb mobile low-power DDR4 SDRAM with low  $V_{\rm DDQ}$  (LPDDR4X) is a high-speed, CMOS dynamic random-access memory device. This device is internally configured with 2 channels or 1 channel ×16 I/O, each channel having 8-banks.

#### **General Notes**

Throughout the data sheet, figures and text refer to DQs as DQ. DQ should be interpreted as any or all DQ collectively, unless stated otherwise.

DQS and CK should be interpreted as DQS\_t, DQS\_c and CK\_t, CK\_c respectively, unless stated otherwise. CA includes all CA pins used for a given density.

In timing diagrams, CMD is used as an indicator only. Actual signals occur on CA[5:0].

$V_{REF}$  indicates  $V_{REFCA}$  and  $V_{REFDQ}$ .

Complete functionality may be described throughout the entire document. Any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

Any specific requirement takes precedence over a general statement.

Any functionality not specifically stated herein is considered undefined, illegal, not supported, and will result in unknown operation.

For single-ended CK and DQS features or specifications, refer to the LPDDR4X Single-Ended CK and DQS Addendum.

# **Device Configuration**

**Table 3: Device Configuration**

|                  |                                         | 4G32 (128 Gb/package)   |  |  |

|------------------|-----------------------------------------|-------------------------|--|--|

| Die organization | Channel A, rank 0 DQ[7:0]_A             | x8 mode × 1 die         |  |  |

| n the package    | Channel A, rank 1 DQ[7:0]_A             | x8 mode × 1 die         |  |  |

|                  | Channel B, rank 0 DQ[7:0]_B             | x8 mode × 1 die         |  |  |

|                  | Channel B, rank 1 DQ[7:0]_B             | x8 mode × 1 die         |  |  |

|                  | Channel A, rank 0 DQ[15:8]_A            | x8 mode × 1 die         |  |  |

|                  | Channel A, rank 1 DQ[15:8]_A            | x8 mode × 1 die         |  |  |

|                  | Channel B, rank 0 DQ[15:8]_B            | x8 mode × 1 die         |  |  |

|                  | Channel B, rank 1 DQ[15:8]_B            | x8 mode × 1 die         |  |  |

| Die addressing   | Dual/single Die                         | 16Gb single-channel die |  |  |

|                  | Memory density (per die)                | 16Gb                    |  |  |

|                  | Memory density (per x8 channel)         | 16Gb                    |  |  |

|                  | Configuration                           | 256Mb × 8 DQ × 8 banks  |  |  |

|                  | Number of channels (per die)            | 1                       |  |  |

|                  | Number of banks (per channel)           | 8                       |  |  |

|                  | Array prefetch (bits, per channel)      | 128                     |  |  |

|                  | Number of rows (per channel)            | 262,144                 |  |  |

|                  | Number of columns<br>(fetch boundaries) | 64                      |  |  |

|                  | Page size (bytes)                       | 1024                    |  |  |

|                  | Channel density (bits per channel)      | 17,179,869,184          |  |  |

|                  | Total density (bits per die)            | 17,179,869,184          |  |  |

|                  | Bank address                            | BA[2:0]                 |  |  |

|                  | Row address                             | R[17:0]                 |  |  |

|                  | Column address                          | C[9:0]                  |  |  |

|                  | Burst starting address boundary         | 64-bit                  |  |  |

- Notes: 1. Refer to Package Block Diagram section in Product specification and SDRAM Addressing section in General LPDDR4X specification.

- 2. Refer to Byte Mode section for further information.

## **Refresh Requirement Parameters**

Table 4: Refresh Requirement Parameters - 16Gb per Channel

| Parameter                      | Symbol             | 16Gb per Channel | Unit |

|--------------------------------|--------------------|------------------|------|

| REFRESH cycle time (all banks) | <sup>t</sup> RFCab | 380              | ns   |

| REFRESH cycle time (per bank)  | <sup>t</sup> RFCpb | 190              | ns   |

200b: x32 LPDDR4X/LPDDR4 SDRAM Product Specification

#### Table 4: Refresh Requirement Parameters - 16Gb per Channel (Continued)

| Parameter                                                  | Symbol               | 16Gb per Channel | Unit |

|------------------------------------------------------------|----------------------|------------------|------|

| Per bank refresh to per bank refresh time (different bank) | <sup>t</sup> PBR2PBR | 90               | ns   |

Note: 1. This table only describes refresh parameters which are density dependent. Refer to Refresh Requirement section in General LPDDR4X specification for all the refresh parameters.

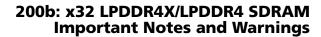

#### **Package Block Diagrams**

Figure 2: Eight-Die, Dual-Channel, Dual-Rank Package Block Diagram

Note: 1. ODTca bond pad for Rank 0, [7:0] byte selected device of each channel is wired to the respective ODT ball. Other ODTca bond pads are wired to V<sub>SS</sub> in the package.

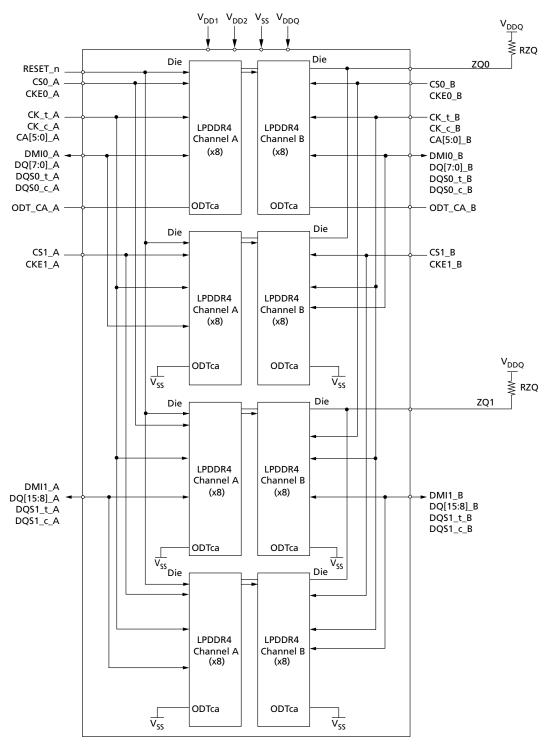

### **Ball Assignments and Descriptions**

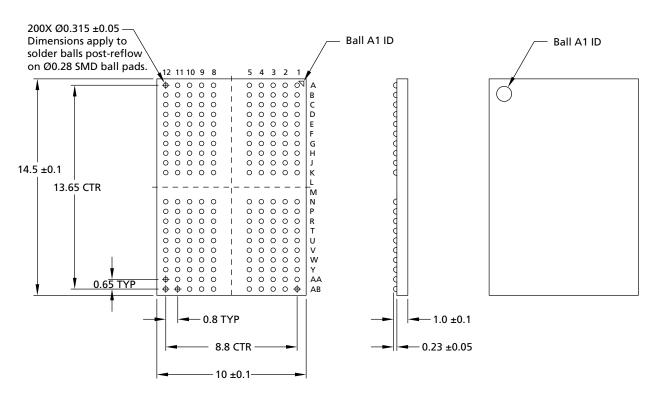

Figure 3: 200-Ball Dual-Channel, Dual-Rank Discrete FBGA

**Table 5: Ball/Pad Descriptions**

| Symbol                                                 | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t_A, CK_c_A,<br>CK_t_B, CK_c_B                      | Input     | <b>Clock:</b> CK_t and CK_c are differential clock inputs. All address, command and control input signals are sampled on positive edge of CK_t and the negative edge of CK_c. AC timings for CA parameters are referenced to clock. Each channel (A, B) has its own clock pair.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CKE0_A, CKE1_A,<br>CKE0_B, CKE1_B                      | Input     | <b>Clock enable:</b> CKE HIGH activates and CKE LOW deactivates the internal clock signals, input buffers, and output drivers. Power-saving modes are entered and exited via CKE transitions. CKE is sampled at the rising edge of CK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CS0_A, CS1_A,<br>CS0_B, CS1_B                          | Input     | Chip select: Each channel (A, B) has its own CS signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CA[5:0]_A,<br>CA[5:0]_B                                | Input     | <b>Command/address inputs:</b> Provide the command and address inputs according to the command truth table. Each channel (A, B) has its own CA signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ODT_CA_A,<br>ODT_CA_B                                  | Input     | <b>LPDDR4 CA ODT control:</b> The ODT_CA pin is used in conjunction with the mode register to turn on/off the on-die termination for CA pins. It is bonded to V <sub>DD2</sub> within the package, or at the package ball, for the terminating rank, and the non-terminating ranks are bonded to V <sub>SS</sub> (or left floating with a weak pull-down on the DRAM die). The terminating rank is the DRAM that terminates the CA bus for all die on the same channel. <b>LPDDR4X CA ODT Control:</b> The ODT_CA pin is ignored by LPDDR4X devices. CA ODT is fully controlled through MR11 and MR22. The ODT_CA pin shall be connected to a valid logic level.                                                                                   |

| DQ[15:0]_A,<br>DQ[15:0]_B                              | I/O       | Data input/output: Bidirectional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DQS[1:0]_t_A, DQS[1:0]_c_A, DQS[1:0]_t_B, DQS[1:0]_c_B | I/O       | <b>Data strobe:</b> DQS_t and DQS_c are bi-directional differential output clock signals used to strobe data during a READ or WRITE. The data strobe is generated by the DRAM for a READ and is edge-aligned with data. The data strobe is generated by the SoC memory controller for a WRITE and is trained to precede data. Each byte of data has a data strobe signal pair. Each channel (A, B) has its own DQS_t and DQS_c strobes.                                                                                                                                                                                                                                                                                                            |

| DMI[1:0]_A,<br>DMI[1:0]_B                              | I/O       | <b>Data mask/Data bus inversion:</b> Data mask inversion (DMI) is a dual use bi-directional signal used to indicate data to be masked, and data which is inverted on the bus. For data bus inversion (DBI), the DMI signal is driven HIGH when the data on the data bus is inverted, or driven LOW when the data is in its normal state. DBI can be disabled via a mode register setting. For data mask, the DMI signal is used in combination with the data lines to indicate data to be masked in a MASK WRITE command (see the Data Mask (DM) and Data Bus Inversion (DBI) sections for details). The data mask function can be disabled via a mode register setting. Each byte of data has a DMI signal. Each channel has its own DMI signals. |

| ZQ0, ZQ1                                               | Reference | <b>ZQ calibration reference:</b> Used to calibrate the output drive strength and the termination resistance. The ZQ pin shall be connected to $V_{DDQ}$ through a 240 $\Omega$ ±1% resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{\rm DDQ}$ , $V_{\rm DD1}$ , $V_{\rm DD2}$          | Supply    | Power supplies: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub>                                        | Supply    | Ground reference: Power supply ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RESET_n                                                | Input     | <b>RESET:</b> When asserted LOW, the RESET pin resets all channels of the die.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DNU                                                    | -         | <b>Do not use:</b> Must be grounded or left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC                                                     | _         | No connect: Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

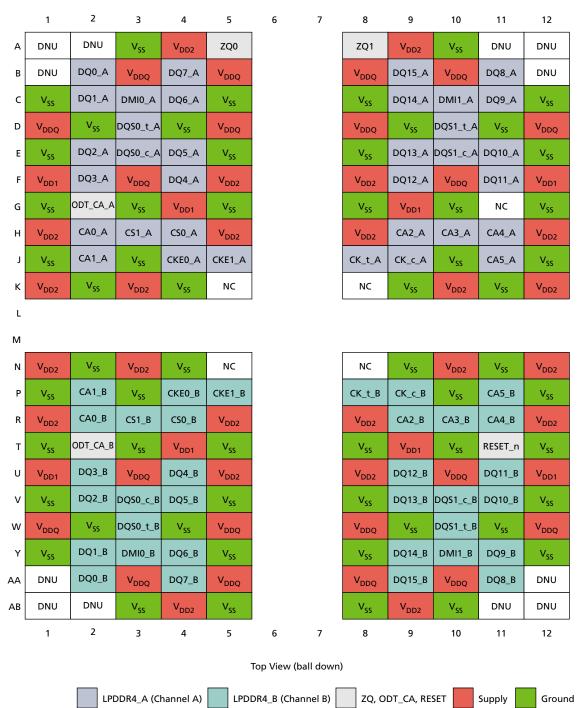

# **Package Dimensions**

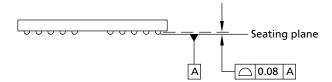

Figure 4: 200-Ball TFBGA - 10mm x 14.5mm x 1.1mm (Package Code: CY)

Notes:

- 1. All dimensions are in millimeters.

- 2. Solder ball composition: SAC302 with NiAu pads (96.8% Sn, 3.0% Ag, 0.2% Cu).

### **Product Specific Mode Register definition**

#### **Table 6: Mode Register Contents**

Notes 1 and 2 apply to entire table.

| Mode Register | OP7         | OP6                                                                                                                                                                       | OP5                      | OP4            | OP3                                                   | OP2                                       | OP1             | OP0    |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------|-------------------------------------------------------|-------------------------------------------|-----------------|--------|

| MR0           |             |                                                                                                                                                                           | Single-<br>ended<br>mode |                |                                                       | RFM sup-<br>port                          | Latency<br>mode | REF    |

|               |             | OP[0] = 1b: Only modified refresh mode supported OP[1] = 0b: Device supports normal latency OP[2] = 0b: Device supports TRR OP[5] = 1b: Device supports single-ended mode |                          |                |                                                       |                                           |                 |        |

| MR3           |             |                                                                                                                                                                           | OP[2] =                  | •              | ection disable                                        |                                           |                 |        |

| MR5           |             | Manufacturer ID  1111 1111b : Micron                                                                                                                                      |                          |                |                                                       |                                           |                 |        |

| MR6           |             | <b>Revision ID1</b> 0000 0111b                                                                                                                                            |                          |                |                                                       |                                           |                 |        |

| MR8           | OP[7        | vidth<br>7:6] =<br>7:channel                                                                                                                                              | OP[5:2]                  |                | Density<br>110b: 16Gb single-channel die              |                                           |                 |        |

| MR13          |             | OP[2] =                                                                                                                                                                   | 0b: Normal o             | •              |                                                       | VRO and V <sub>REF(DO)</sub> value on DQ6 |                 |        |

| MR24          | TRR<br>mode |                                                                                                                                                                           |                          |                | Unlimited MAC                                         |                                           | MAC value       |        |

|               |             |                                                                                                                                                                           |                          | DP[7] = 0b: Di | : Unlimited N<br>sable (defaul <sup>.</sup><br>served |                                           |                 |        |

| MR25          |             |                                                                                                                                                                           |                          | PPR res        | ources <sup>4</sup>                                   |                                           |                 |        |

|               | Bank 7      | Bank 6                                                                                                                                                                    | Bank 5                   |                | Bank 3<br>urce is not av<br>urce is availal           |                                           | Bank 1          | Bank 0 |

- Notes: 1. The contents of Product Specific Mode Register definition will reflect information specific to each die in these packages.

- 2. Other bits not defined above and other mode registers are referred to Mode Register Assignments and Definitions section.

- 3. When not using PPR function, PPR protection should be enabled to prevent unintended PPR entry.(MR3 OP[2] = 1b).

- 4. Before using PPR function, confirm the availability of PPR resource by reading MR25.

# **I<sub>DD</sub> Parameters**

Refer to  $I_{DD}$  Specification Parameters and Test Conditions section for detailed conditions.

# Table 7: I<sub>DD</sub> Parameters – Single Die (16Gb Single-Channel Die)

$V_{DD2}$ = 1.06–1.17V;  $V_{DDO}$  = 0.57–0.65V;  $V_{DD1}$  = 1.70–1.95V;  $T_C$  = -25°C to +85°C

|                     | 0.57–0.65V; V <sub>DD1</sub> = 1.70–1.95V; T <sub>C</sub> = −2 | Speed Grade |      |      |

|---------------------|----------------------------------------------------------------|-------------|------|------|

| Symbol              | Supply                                                         | 4266 Mb/s   | Unit | Note |

| DD01                | $V_{DD1}$                                                      | 5.00        | mA   |      |

| DD02                | $V_{DD2}$                                                      | 26.00       |      |      |

| I <sub>DD0Q</sub>   | $V_{DDQ}$                                                      | 0.75        |      |      |

| I <sub>DD2P1</sub>  | $V_{DD1}$                                                      | 2.40        | mA   |      |

| DD2P2               | $V_{DD2}$                                                      | 3.40        |      |      |

| DD2PQ               | $V_{DDQ}$                                                      | 0.75        |      |      |

| DD2PS1              | $V_{DD1}$                                                      | 2.40        | mA   |      |

| DD2PS2              | $V_{DD2}$                                                      | 3.40        |      |      |

| DD2PSQ              | $V_{DDQ}$                                                      | 0.75        |      |      |

| DD2N1               | V <sub>DD1</sub>                                               | 2.40        | mA   |      |

| I <sub>DD2N2</sub>  | $V_{DD2}$                                                      | 14.00       |      |      |

| DD2NQ               | $V_{DDQ}$                                                      | 0.75        |      |      |

| I <sub>DD2NS1</sub> | $V_{DD1}$                                                      | 2.40        | mA   |      |

| DD2NS2              | $V_{DD2}$                                                      | 12.00       |      |      |

| DD2NSQ              | $V_{DDQ}$                                                      | 0.75        |      |      |

| DD3P1               | $V_{DD1}$                                                      | 2.40        | mA   |      |

| DD3P2               | $V_{DD2}$                                                      | 6.20        |      |      |

| DD3PQ               | $V_{DDQ}$                                                      | 0.75        |      |      |

| DD3PS1              | $V_{DD1}$                                                      | 2.40        | mA   |      |

| DD3PS2              | $V_{DD2}$                                                      | 6.20        |      |      |

| DD3PSQ              | $V_{DDQ}$                                                      | 0.75        |      |      |

| DD3N1               | $V_{DD1}$                                                      | 3.40        | mA   |      |

| I <sub>DD3N2</sub>  | $V_{DD2}$                                                      | 16.00       |      |      |

| DD3NQ               | $V_{DDQ}$                                                      | 0.75        |      |      |

| DD3NS1              | $V_{DD1}$                                                      | 3.40        | mA   |      |

| DD3NS2              | $V_{DD2}$                                                      | 14.00       |      |      |

| DD3NSQ              | $V_{DDQ}$                                                      | 0.75        |      |      |

| DD4R1               | V <sub>DD1</sub>                                               | 11.00       | mA   | 2, 3 |

| DD4R2               | $V_{DD2}$                                                      | 205.00      |      |      |

| DD4RQ               | $V_{DDQ}$                                                      | 63.00       |      |      |

| DD4W1               | V <sub>DD1</sub>                                               | 11.00       | mA   | 2    |

| DD4W2               | $V_{DD2}$                                                      | 160.00      |      |      |

| I <sub>DD4WQ</sub>  | $V_{DDQ}$                                                      | 0.75        |      |      |

#### Table 7: I<sub>DD</sub> Parameters - Single Die (16Gb Single-Channel Die) (Continued)

$V_{DD2}$ = 1.06–1.17V;  $V_{DDO}$  = 0.57–0.65V;  $V_{DD1}$  = 1.70–1.95V;  $T_C$  = -25°C to +85°C

|                     |                    | Speed Grade |      |      |

|---------------------|--------------------|-------------|------|------|

| Symbol              | Supply             | 4266 Mb/s   | Unit | Note |

| I <sub>DD51</sub>   | V <sub>DD1</sub>   | 23.00       | mA   |      |

| I <sub>DD52</sub>   | V <sub>DD2</sub>   | 110.00      |      |      |

| I <sub>DD5Q</sub>   | $V_{DDQ}$          | 0.75        |      |      |

| I <sub>DD5AB1</sub> | V <sub>DD1</sub>   | 6.60        | mA   |      |

| I <sub>DD5AB2</sub> | V <sub>DD2</sub>   | 24.00       |      |      |

| I <sub>DD5ABQ</sub> | $V_{DDQ}$          | 0.75        |      |      |

| I <sub>DD5PB1</sub> | V <sub>DD1</sub>   | 4.80        | mA   |      |

| I <sub>DD5PB2</sub> | V <sub>DD2</sub>   | 24.00       |      |      |

| I <sub>DD5PBQ</sub> | $V_{\mathrm{DDQ}}$ | 0.75        |      |      |

- Notes: 1. Published I<sub>DD</sub> values except I<sub>DD4RQ</sub> are the maximum I<sub>DD</sub> values considering the worstcase conditions of process, temperature, and voltage.

- 2. BL = 16, DBI disabled.

- 3.  $I_{DD4RQ}$  value is reference only. Typical value.  $V_{OH} = 0.5 \times V_{DDQ}$ ;  $T_{C} = 25^{\circ}C$

#### Table 8: I<sub>DD6</sub> Full-Array Self Refresh Current - Single Die (16Gb Single-Channel Die)

$V_{DD2} = 1.06 - 1.17V$ ;  $V_{DDO} = 0.57 - 0.65V$ ;  $V_{DD1} = 1.70 - 1.95V$

| Temperature | Supply             | Full-Array Self Refresh Current | Unit |

|-------------|--------------------|---------------------------------|------|

| 25°C        | V <sub>DD1</sub>   | 0.52                            | mA   |

|             | $V_{DD2}$          | 1.16                            |      |

|             | $V_{\mathrm{DDQ}}$ | 0.01                            |      |

| 85°C        | V <sub>DD1</sub>   | 4.30                            | mA   |

|             | $V_{DD2}$          | 9.00                            |      |

|             | $V_{\mathrm{DDQ}}$ | 0.75                            |      |

Note: 1.  $I_{DD6}$  25°C is the typical value in the distribution with nominal  $V_{DD}$  and a reference-only value. I<sub>DD6</sub> 85°C is the maximum I<sub>DD</sub> guaranteed value considering the worst-case conditions of process, temperature, and voltage.