# Intel<sup>®</sup> Arria<sup>®</sup> 10 GX, GT, and SX Device Family Pin Connection Guidelines

# **Contents**

| Intel® Arria® 10 GX, GT, and SX Device Family Pin Connection Guidelines                             | 3  |

|-----------------------------------------------------------------------------------------------------|----|

| Intel® Arria® 10 GX and GT Pin Connection Guidelines                                                |    |

| Clock and PLL Pins                                                                                  |    |

| Dedicated Configuration/JTAG Pins                                                                   |    |

| Optional/Dual-Purpose Configuration Pins                                                            |    |

| Partial Reconfiguration Pins                                                                        |    |

| Differential I/O Pins.                                                                              |    |

| External Memory Interface and Hard Memory PHY Pins                                                  |    |

| Reference Pins                                                                                      |    |

| Voltage Sensor Pins                                                                                 |    |

| Supply Pins                                                                                         |    |

| Transceiver Pins                                                                                    |    |

| Intel Arria 10 SX Pin Connection Guidelines                                                         |    |

| HPS Supply Pins                                                                                     |    |

| HPS Dedicated I/O Bank Pins                                                                         |    |

| HPS Peripheral Pins                                                                                 | 31 |

| Shared 3V I/O Bank Pins                                                                             | 37 |

| Power Supply Sharing Guidelines for Intel Arria 10 Devices                                          | 61 |

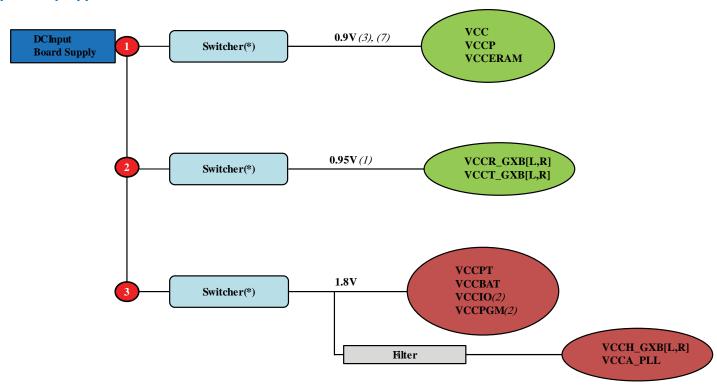

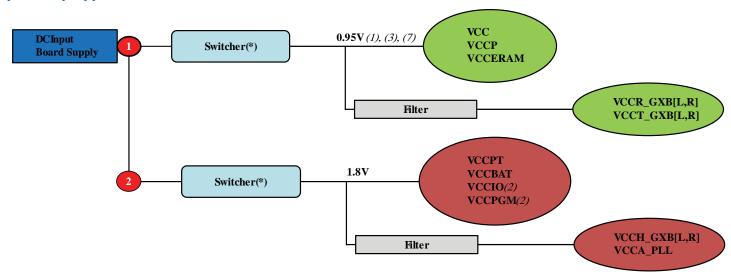

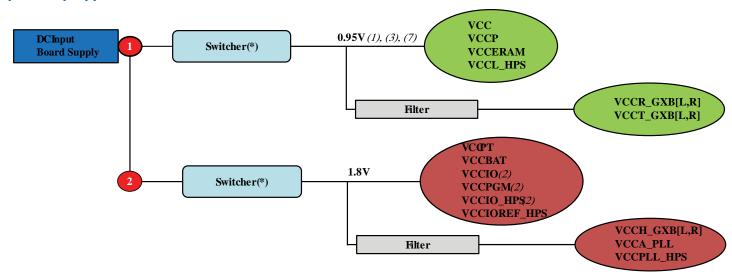

| Example 1—Intel Arria 10 GX                                                                         |    |

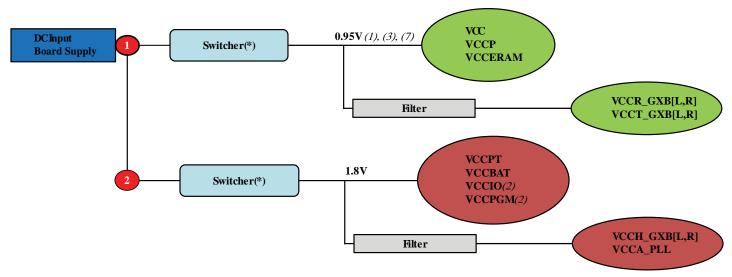

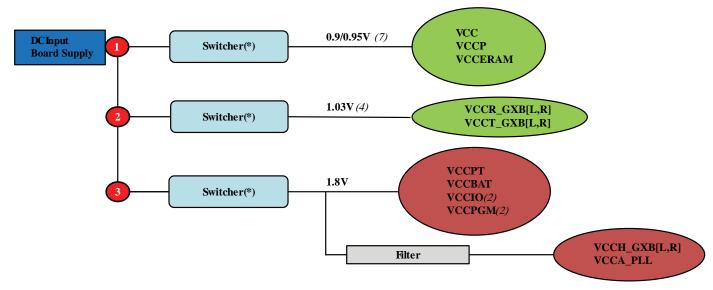

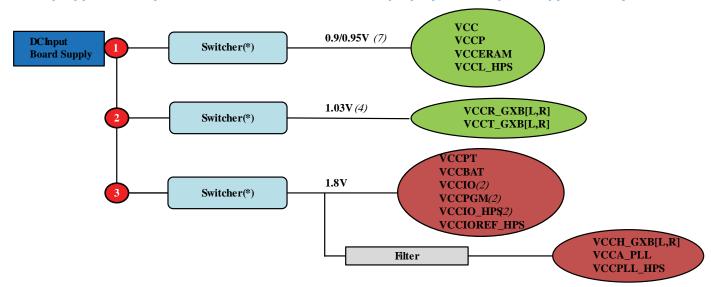

| Example 2—Intel Arria 10 GX                                                                         | 64 |

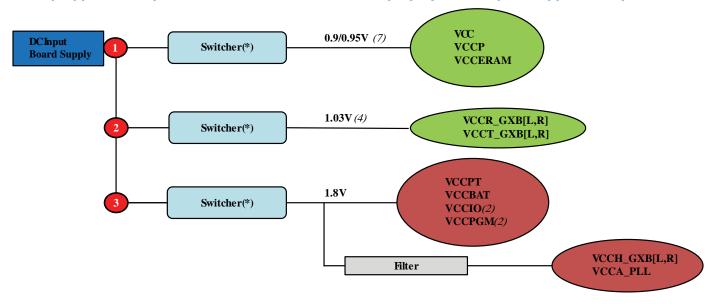

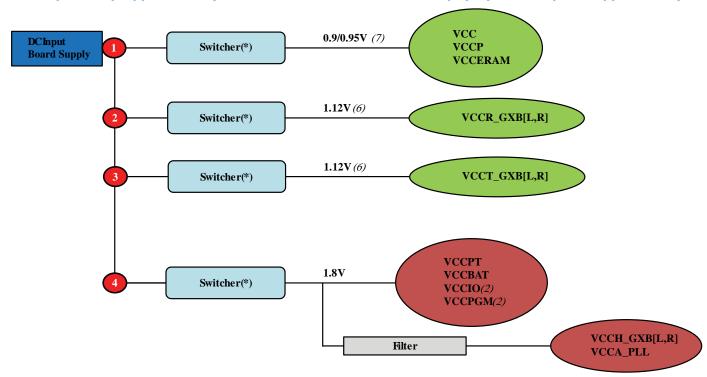

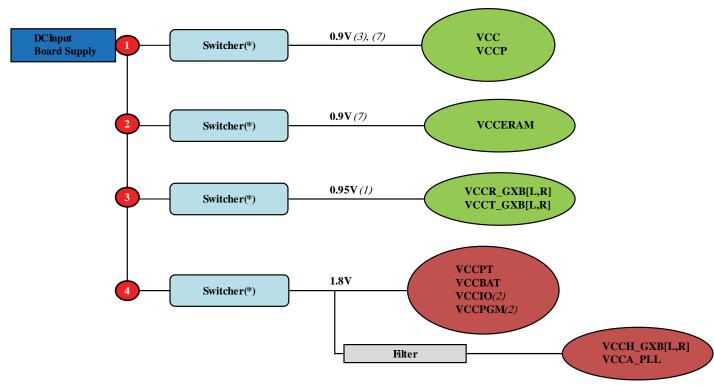

| Example 3—Intel Arria 10 GX                                                                         | 66 |

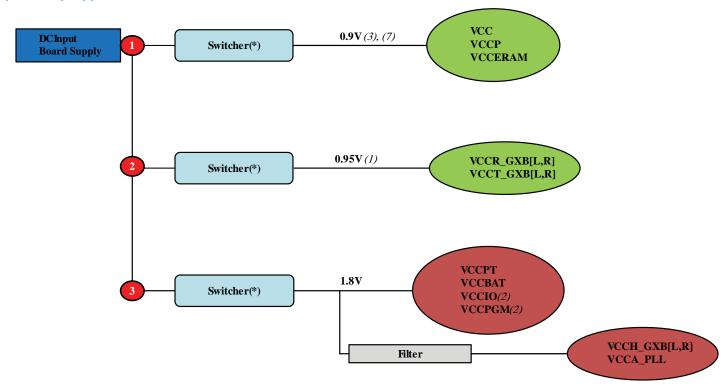

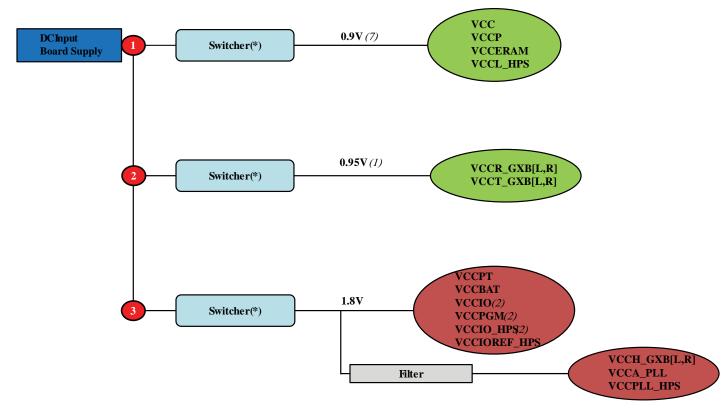

| Example 4—Intel Arria 10 GT                                                                         | 68 |

| Example 5—Intel Arria 10 GT                                                                         | 71 |

| Example 6—Intel Arria 10 GT                                                                         | 73 |

| Example 7—Intel Arria 10 GT                                                                         | 75 |

| Example 8—Intel Arria 10 SX                                                                         | 78 |

| Example 9—Intel Arria 10 SX                                                                         | 81 |

| Example 10—Intel Arria 10 SX                                                                        | 83 |

| Example 11—Intel Arria 10 GX (Using the SmartVID Feature)                                           |    |

| Notes to Power Supply Sharing Guidelines                                                            |    |

| Document Revision History for Intel Arria 10 GX, GT, and SX Device Family Pin Connection Guidelines | 90 |

#### Disclaimer

© 2018 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, NIOS, Quartus Prime and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. These pin connection guidelines, and your use thereof, are subject to and governed by Intel's terms and conditions below. By using these pin connection guidelines, you indicate your accept - ance of all such terms and conditions. If you do not agree with such terms and conditions, you may not use the pin connection guidelines, and you are required to promptly and irrevocably destroy the pin connection guidelines and any copies or portions thereof in your possession or under your control.

#### Terms and Conditions:

- 1. These pin connection guidelines are provided as examples only, and should not be deemed to be technical specifications or recommendations. The use of the pin connection guidelines for any particular design should be verified for device operation with the applicable datasheet and Intel.

- 2. Subject to these terms and conditions, Intel grants to you the use of these pin connection guidelines as examples of possible pin connections of an Intel programmable logic device-based design. You may not use these pin connection guidelines for any other purpose except as expressly permitted in these terms and conditions. Intel does not recommend, suggest, or require that these pin connection guidelines be used in conjunction or combination with any other software or product, and makes no representations, warranties or guaranties, implied or express as well as any warranties arising from course of performance, course of dealing, or usage in trade including but not limited to the accuracy, completeness or genuineness thereof.

- 3. Intel will not be liable for any lost revenue, lost profits, or other consequential, indirect, or special damages caused by your use of these pin connection guidelines even if advised of the possibility of such damages occurring.

- 4. This agreement shall be governed in all respects by the laws of the State of Delaware, without regard to conflict of law or choice of law principles. You agree to submit to the exclusive jurisdiction of the federal and state courts in the State of Delaware for the resolution of any dispute or claim arising out of or relating to these terms of use.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Intel® Arria® 10 GX and GT Pin Connection Guidelines

## **Clock and PLL Pins**

Note:

Table 1. Clock and PLL Pins

| Pin Name                                    | Pin<br>Functions    | Pin Description                                                                                                                                                                                                                            | Connection Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_[2,3] [A,B,C,D,E,F,G,H,I,J,K,L]_[0,1]p  | I/O, Clock<br>Input | Dedicated high speed clock input pins that can be used for data inputs or outputs. Differential input OCT $R_{\text{D}}$ , single-ended input OCT $R_{\text{T}}$ , and single-ended output OCT $R_{\text{S}}$ are supported on these pins. | Tie the unused pins to GND or leave them unconnected. If the pins are not connected, use the Intel Quartus Prime software programmable options to internally bias these pins. These pins can be reserved as inputs tristate with weak pull-up resistor enabled, or as outputs driving GND.  If you are using the Early I/O Release feature in the Intel Arria® 10 SX devices, ensure that the input clock to the HPS SDRAM IP is located within the active HPS I/O banks. For more information, refer to the HPS EMIF Design Consideration chapter of the Intel Arria 10 SoC Design Guidelines. |

| CLK_[2,3] [A,B,C,D,E,F,G,H,I,J,K,L]_[0,1]n  | I/O, Clock<br>Input | Dedicated high speed clock input pins that can be used for data inputs or outputs. Differential input OCT $R_{\text{D}}$ , single-ended input OCT $R_{\text{T}}$ , and single-ended output OCT $R_{\text{S}}$ are supported on these pins. | Tie the unused pins to GND or leave them unconnected. If the pins are not connected, use the Intel Quartus Prime software programmable options to internally bias these pins. These pins can be reserved as inputs tristate with weak pull-up resistor enabled, or as outputs driving GND.  If you are using the Early I/O Release feature in the Intel Arria 10 SX devices, ensure that the input clock to the HPS SDRAM IP is located within the active HPS I/O banks. For more information, refer to the HPS EMIF Design Consideration chapter of the Intel Arria 10 SoC Design Guidelines.  |

| PLL_[2,3] [A,B,C,D,E,F,G,H,I,J,K,L]_FB[0,1] | I/O, Clock          | Dual-purpose I/O pins that can be used as single-ended inputs, single-ended outputs, or external feedback input pin. For more information about the supported pins, refer to the device pinout file.                                       | Tie the unused pins to GND or leave them unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                             |                     |                                                                                                                                                                                                                                            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin Name                                                                                            | Pin<br>Functions | Pin Description                                                                                                                                                                        | Connection Guidelines                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                     |                  |                                                                                                                                                                                        | If the pins are not connected, use the Intel Quartus Prime software programmable options to internally bias these pins. These pins can be reserved as inputs tristate with weak pullup resistor enabled, or as outputs driving GND.                                                         |

| PLL_[2,3] [A,B,C,D,E,F,G,H,I,J,K ,L]_CLKOUT[0:1], PLL_[2,3] [A,B,C,D,E,F,G,H,I,J,K ,L]_CLKOUT[0:1]p | I/O, Clock       | I/O pins that can be used as two single-ended clock output pins or one differential clock output pair. For more information about the supported pins, refer to the device pinout file. | Tie the unused pins to GND or leave them unconnected.  If the pins are not connected, use the Intel Quartus Prime software programmable options to internally bias these pins. These pins can be reserved as inputs tristate with weak pull-up resistor enabled, or as outputs driving GND. |

| PLL_[2,3] [A,B,C,D,E,F,G,H,I,J,K,L]_CLKOUT[0:1]n                                                    | I/O, Clock       | I/O pins that can be used as two single-ended clock output pins or one differential clock output pair. For more information about the supported pins, refer to the device pinout file. | Tie the unused pins to GND or leave them unconnected.  If the pins are not connected, use the Intel Quartus Prime software programmable options to internally bias these pins. These pins can be reserved as inputs tristate with weak pull-up resistor enabled, or as outputs driving GND. |

## **Dedicated Configuration/JTAG Pins**

Note:

Intel recommends that you create a Intel Quartus Prime design, enter your device I/O assignments, and compile the design. The Intel Quartus Prime software will check your pin connections according to I/O assignment and placement rules. The rules differ from one device to another based on device density, package, I/O assignments, voltage assignments, and other factors that are not fully described in this document or the device handbook.

## **Table 2. Dedicated Configuration/JTAG Pins**

| Pin Name   | Pin Functions | Pin Description                                                                                                                                                                                                                                                                                  | Connection Guidelines                                                                                                                                                                                                                                                             |

|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nIO_PULLUP | Input         | Dedicated input pin that determines the internal pull-ups on user I/O pins and dual-purpose I/O pins (DATA[0:31], CLKUSR, INIT_DONE, DEV_CE, and DEV_CLRn) are on or off before and during configuration.  A logic high turns off the weak pull-up, while a logic low turns on the weak pull-up. | Tie the nio-pullup pin directly to VCC using a 1 k $\Omega$ pullup resistor, or directly to GND. This pin has an internal 25-k $\Omega$ pull-down. If you tie this pin to VCC, ensure all user I/O pins and dual-purpose I/O pins are at logic-0 before and during configuration. |

| TEMPDIODEP | Input         | Pin used for temperature sensing diode (bias-high input) inside the FPGA.                                                                                                                                                                                                                        | If you do not use the temperature sensing diode with an external temperature sensing device, connect this pin to GND.                                                                                                                                                             |

#### PCG-01017 | 2018.03.30

| Pin Name   | Pin Functions                  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                    | Connection Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEMPDIODEn | Input                          | Pin used for temperature sensing diode (bias-low input) inside the FPGA.                                                                                                                                                                                                                                                                                                                                           | If you do not use the temperature sensing diode with an external temperature sensing device, connect this pin to GND.                                                                                                                                                                                                                                                                                                                                                                        |

| MSEL[0:2]  | Input                          | Configuration input pins that set the configuration scheme for the FPGA device.                                                                                                                                                                                                                                                                                                                                    | These pins are internally connected through a $25\text{-k}\Omega$ resistor to GND. Do not leave these pins floating. When these pins are unused, connect them to GND. Depending on the configuration scheme used, tie these pins to VCCPGM or GND. For more information about the configuration scheme options, refer to the Configuration, Design Security, and Remote System Upgrades for Intel Arria 10 Devices chapter. If you use JTAG configuration scheme, connect these pins to GND. |

| nCE        | Input                          | Dedicated active-low chip enable pin. When the nCE pin is low, the device is enabled. When the nCE pin is high, the device is disabled.                                                                                                                                                                                                                                                                            | In multi-device configuration, the nCE pin of the first device is tied low while its nCEO pin drives the nCE pin of the next device in the chain.  In single-device configuration and JTAG programming, connect the nCE pin to GND.                                                                                                                                                                                                                                                          |

| nCONFIG    | Input                          | Dedicated configuration control input pin. Pulling this pin low during user mode causes the FPGA to lose its configuration data, enter a reset state, and tri-state all I/O pins. Returning this pin to a logic high level initiates reconfiguration.                                                                                                                                                              | Connect the nCONFIG pin directly to the configuration controller when the FPGA uses a passive configuration scheme. Connect the nCONFIG pin through a 10-k $\Omega$ resistor tied to VCCPGM when the FPGA uses an active serial (AS) configuration scheme. If you do not use this pin, connect the pin directly or through a 10-k $\Omega$ resistor to VCCPGM.                                                                                                                               |

| CONF_DONE  | Bidirectional (open-<br>drain) | Dedicated configuration done pin.  As a status output, the CONF_DONE pin drives low before and during configuration. After all configuration data is received without error and the initialization cycle starts, CONF_DONE is released.  As a status input, the CONF_DONE pin goes high after all data is received. Then the device initializes and enters user mode. This pin is not available as a user I/O pin. | Connect an external 10-k $\Omega$ pull-up resistors to VCCPGM. VCCPGM must be high enough to meet the VIH specification of the I/O on the device and the external host. When you use passive configuration schemes, the configuration controller monitors this pin.                                                                                                                                                                                                                          |

| nCEO       | I/O, Output (opendrain)        | When device configuration is complete, the nCEO pin drives low.  If you do not use this pin as a configuration pin, you can use this pin as a user I/O pin.                                                                                                                                                                                                                                                        | In multi-device configuration, the nCEO pin feeds the nCE pin of a subsequent FPGA. Connect this pin through an external 10-k $\Omega$ pull-up resistor to VCCPGM.                                                                                                                                                                                                                                                                                                                           |

|            | ·                              |                                                                                                                                                                                                                                                                                                                                                                                                                    | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin Name | Pin Functions              | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                          | Connection Guidelines                                                                                                                                                                                                                                                                                                                                     |

|----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | In single-device configuration, you can leave this pin floating.                                                                                                                                                                                                                                                                                          |

| nSTATUS  | Bidirectional (open-drain) | Dedicated configuration status pin. The FPGA drives the nSTATUS pin low immediately after power-up, and releases the pin after power-on reset (POR) time.  As a status output, the nSTATUS pin is pulled low if an error occurs during configuration.  As a status input, the device enters an error state when the nSTATUS pin is driven low by an external source during configuration or initialization. This pin is not available as a user I/O pin. | Connect an external $10\text{-}k\Omega$ pull-up resistors to VCCPGM. VCCPGM must be high enough to meet the VIH specification of the I/O on the device and the external host. When you use passive configuration schemes, the configuration controller monitors this pin.                                                                                 |

| TCK      | Input                      | Dedicated JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                     | Connect this pin through a 1-k $\Omega$ pull-down resistor to GND. This pin has an internal 25-k $\Omega$ pull-down. Do not drive voltage higher than 1.8-, 1.5-, or 1.2-V VCCPGM supply for the TCK pin. The TCK input pin is powered by the VCCPGM supply.                                                                                              |

| TMS      | Input                      | Dedicated JTAG test mode select input pin.                                                                                                                                                                                                                                                                                                                                                                                                               | Connect this pin to a 1–10-k $\Omega$ pull-up resistor to VCCPGM. If the JTAG interface is not used, connect the TMS pin to VCCPGM using a 1-k $\Omega$ resistor. This pin has an internal 25-k $\Omega$ pull-up. Do not drive voltage higher than 1.8-, 1.5-, or 1.2-V VCCPGM supply for the TMS pin. The TMS input pin is powered by the VCCPGM supply. |

| TDI      | Input                      | Dedicated JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                      | Connect this pin to a 1–10-k $\Omega$ pull-up resistor to VCCPGM. If the JTAG interface is not used, connect the TDI pin to VCCPGM using a 1-k $\Omega$ resistor. This pin has an internal 25-k $\Omega$ pull-up. Do not drive voltage higher than 1.8-, 1.5-, or 1.2-V VCCPGM supply for the TDI pin. The TDI input pin is powered by the VCCPGM supply. |

| TDO      | Output                     | Dedicated JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                                                     | If the JTAG interface is not used, leave the TDO pin unconnected.                                                                                                                                                                                                                                                                                         |

| TRST     | Input                      | Dedicated active low JTAG test reset input pin. The TRST pin is used to asynchronously reset the JTAG boundary-scan circuit.                                                                                                                                                                                                                                                                                                                             | Utilization of the TRST pin is optional. If you do not use this pin, tie this pin through a 1-k $\Omega$ pull-up resistor to VCCPGM.                                                                                                                                                                                                                      |

|          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | continued                                                                                                                                                                                                                                                                                                                                                 |

| Pin Name  | Pin Functions | Pin Description                                                                                                               | Connection Guidelines                                                                                                                                                      |

|-----------|---------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |               |                                                                                                                               | When you use this pin, ensure that the TMS pin is held high or the TCK pin is static when the TRST pin is changing from low to high.                                       |

|           |               |                                                                                                                               | To disable the JTAG circuitry, tie this pin to $\mbox{GND}.$ This pin has an internal $25-\mbox{k}\Omega$ pull-up.                                                         |

|           |               |                                                                                                                               | Do not drive voltage higher than 1.8-, 1.5-, or 1.2-V VCCPGM supply for the TRST pin. The TRST input pin is powered by the VCCPGM supply.                                  |

| nCSO[0:2] | Output        | Dedicated output control signal from the FPGA to the EPCQ-L device in AS configuration scheme that enables the EPCQ-L device. | When you are not programming the FPGA in the AS configuration scheme, the nCSO pin is not used. When you do not use this pin as an output pin, leave this pin unconnected. |

## **Optional/Dual-Purpose Configuration Pins**

Note:

Table 3. Optional/Dual-Purpose Configuration Pins

| Pin Name  | Pin<br>Functions                   | Pin Description                                                                                                                                                                                                                                                                                                                                                                        | Connection Guidelines                                                                                                                                                                                                                                                                                                                                                          |

|-----------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCLK      | Input (PS,<br>FPP); Output<br>(AS) | Dedicated configuration clock pin. In passive serial (PS) and fast passive parallel (FPP) configuration schemes, DCLK is used to clock configuration data from an external source into the FPGA.  In the AS configuration scheme, DCLK is an output from the FPGA that provides timing for the configuration interface.                                                                | Do not leave this pin floating. Drive this pin either high or low.                                                                                                                                                                                                                                                                                                             |

| CRC_ERROR | I/O, Output<br>(open-drain)        | Active high signal indicates the error detection circuit has detected errors in the configuration RAM (CRAM) bits. Falling edge of this signal indicates the information about the error location and type are available in the error message register (EMR). This dual-purpose pin is only used when you enable error detection in user mode. This pin can be used as a user I/O pin. | When you use the open-drain output dedicated CRC_ERROR pin as an optional pin, connect this pin through an external $10\text{-}k\Omega$ pull-up resistor to VCCPGM. When you do not use the open-drain output dual-purpose CRC_ERROR pin as an optional pin, and the CRC_ERROR pin is not used as an I/O pin, connect this pin as defined in the Intel Quartus Prime software. |

|           | '                                  | <u>'</u>                                                                                                                                                                                                                                                                                                                                                                               | continued                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Name         | Pin<br>Functions            | Pin Description                                                                                                                                                                                                                                                                                                                       | Connection Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEV_CLRn         | I/O, Input                  | Optional pin that allows you to override all clears on all device registers.  When this pin is driven low, all registers are cleared. When this pin is driven high (VCCPGM), all registers behave as programmed.                                                                                                                      | When you do not use the dual-purpose $\mathtt{DEV\_CLRn}$ pin and when this pin is not used as an I/O pin, tie this pin to $\mathtt{GND}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DEV_OE           | I/O, Input                  | Optional pin that allows you to override all tri-states on the device.  When this pin is driven low, all I/O pins are tri-stated. When this pin is driven high (VCCPGM), all I/O pins behave as programmed.                                                                                                                           | When you do not use the dual-purpose DEV_OE pin and when this pin is not used as an I/O pin, tie this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DATA0            | I/O, Input                  | Dual-purpose configuration data input pin. You can use the DATAO pin for PS or FPP configuration scheme, or as an I/O pin after configuration is complete.                                                                                                                                                                            | When you do not use the dedicated input DATAO pin and when this pin is not used as an I/O pin, leave this pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DATA[1:31]       | I/O, Input                  | Dual-purpose configuration data input pins.  Use DATA [1:7] pins for FPP x8, DATA [1:15] pins for FPP x16, and DATA [1:31] pins for FPP x32 configuration or as regular I/O pins. These pins can also be used as user I/O pins after configuration.                                                                                   | When you do not use the dual-purpose DATA[1:31] pins and when these pins are not used as I/O pins, leave these pins unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INIT_DONE        | I/O, Output<br>(open-drain) | This is a dual-purpose pin and can be used as an I/O pin when not enabled as the INIT_DONE pin.  When you enable this pin, a transition from low to high at the pin indicates the device has entered user mode. If the INIT_DONE output is enabled, the INIT_DONE pin cannot be used as a user I/O pin after configuration.           | When you use the optionally open-drain output dedicated INIT_DONE pin, connect this pin to an external 10-k $\Omega$ pull-up resistor to VCCPGM. When you use this pin in an AS or PS multi-device configuration mode, ensure you enable the INIT_DONE pin in the Intel Quartus Prime designs. When you do not use the dedicated INIT_DONE optionally open-drain output, and when this pin is not used as an I/O pin, connect this pin as defined in the Intel Quartus Prime software.                                                                                         |

| nPERST[L,R][0:1] | I/O, Input                  | Dual-purpose fundamental reset pin that is only available when you use together with PCI Express* (PCIe*) hard IP (HIP).  When the pin is low, the transceivers are in reset. When the pin is high, the transceivers are out of reset. When you do not use this pin as the fundamental reset, you can use this pin as a user I/O pin. | Connect this pin as defined in the Intel Quartus Prime software. This pin is powered by 1.8V VCCIO supply and must be driven by 1.8V compatible I/O standards.  Connect the PCIe nPERST pin to a level translator to shift down the voltage from 3.3V LVTTL to 1.8V to interface with this pin. When this pin is not used for configuration purpose, you have the option to select 1.2V, 1.5V, or 1.8V compatible I/O standard. However, you must shift down the 3.3V LVTTL voltage from the PCIe nPERST pin to the selected Intel Arria 10 nPERST I/O standard voltage level. |

|                  | ·                           |                                                                                                                                                                                                                                                                                                                                       | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Name      | Pin<br>Functions | Pin Description                                                                                                                                                                            | Connection Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                  |                                                                                                                                                                                            | Only one nPERST pin is used per PCIe HIP. The Intel Arria 10 components always have all four pins listed even when the specific component might only have 1 or 2 PCIe HIPs.  • nPERSTL0 = Bottom Left PCIe HIP & CvP  • nPERSTL1 = Top Left PCIe HIP (When available)  • nPERSTR0 = Bottom Right PCIe HIP (When available)  • nPERSTR1 = Top Right PCIe HIP (When available)  For maximum compatibility, always use the bottom left PCIe HIP first, as this is the only location that supports Configuration via Protocol (CvP) using the PCIe link. |

| AS_DATAO/ASDO | Bidirectional    | Dedicated AS configuration pin. When using an EPCQ-L device (x1 mode), this is the ASDO pin and is used to send address and control signals between the FPGA device and the EPCQ-L device. | When you do not program the device in the AS configuration mode, the ASDO pin is not used. When you do not use this pin, leave the pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                  |

| AS_DATA[1:3]  | Bidirectional    | Dedicated AS configuration data pins. Configuration data is transported on these pins when connected to the EPCQ-L devices.                                                                | When you do not use this pin, leave the pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **Partial Reconfiguration Pins**

Note:

Intel recommends that you create a Intel Quartus Prime design, enter your device I/O assignments, and compile the design. The Intel Quartus Prime software will check your pin connections according to I/O assignment and placement rules. The rules differ from one device to another based on device density, package, I/O assignments, voltage assignments, and other factors that are not fully described in this document or the device handbook.

## **Table 4.** Partial Reconfiguration Pins

| Pin Name   | Pin<br>Functions | Pin Description                                                                                                                        | Connection Guidelines                                                                                                     |

|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| PR_REQUEST | I/O, Input       | Partial reconfiguration request pin.  Drive this pin high to start partial reconfiguration. Drive this pin low to end reconfiguration. | When you do not use the dedicated input PR_REQUEST pin, and when this pin is not used as an I/O pin, tie this pin to GND. |

|            |                  |                                                                                                                                        | continued                                                                                                                 |

| Pin Name     | Pin<br>Functions                         | Pin Description                                                                                                                                                                                                                             | Connection Guidelines                                                                                                                                                                                                                                                                                                                                                                |

|--------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                          | You can only use this pin in partial reconfiguration using an external host mode in FPP x16 configuration scheme.                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                      |

| PR_READY     | I/O, Output<br>or Output<br>(open-drain) | The partial reconfiguration ready pin is driven low until the device is ready to begin partial reconfiguration. When the device is ready to start reconfiguration, this signal is released and pulled high by an external pull-up resistor. | When you use as optionally open-drain output dedicated $PR\_READY$ pin, connect this pin to an external $10$ -k $\Omega$ pull-up resistor to $VCCPGM$ . When you do not use as the dedicated $PR\_READY$ optionally open-drain output, and when this pin is not used as an $I/O$ pin, connect this pin as defined in the Intel Quartus Prime software.                               |

| PR_ERROR     | I/O, Output<br>or Output<br>(open-drain) | The partial reconfiguration error pin is driven low during partial reconfiguration unless the device detects an error. If an error is detected, this signal is released and pulled high by an external pull-up resistor.                    | When you use as optionally open-drain output dedicated $PR\_ERROR$ pin, connect this pin to an external $10\text{-}k\Omega$ pull-up resistor to VCCPGM. When you do not use as the dedicated $PR\_ERROR$ optionally open-drain output, and when this pin is not used as an I/O pin, connect this pin as defined in the Intel Quartus Prime software.                                 |

| PR_DONE      | I/O, Output<br>or Output<br>(open-drain) | The partial reconfiguration done pin is driven low until the partial reconfiguration is complete. When the reconfiguration is complete, this signal is released and pulled high by an external pull-up resistor.                            | When you use as optionally open-drain output dedicated $PR\_DONE$ pin, connect this pin to an external 10-k $\Omega$ pull-up resistor to VCCPGM. When you do not use as the dedicated $PR\_DONE$ optionally open-drain output, and when this pin is not used as an I/O pin, connect this pin as defined in the Intel Quartus Prime software.                                         |

| CvP_CONFDONE | I/O, Output<br>(open-drain)              | CvP done pin is driven low during configuration. When the CvP configuration is complete, this signal is released and pulled high by an external pull-up resistor.  Status of this pin is only valid if the CONF_DONE pin is high.           | When you use as optionally open-drain output dedicated $\text{CvP\_COMFDONE}$ pin, connect this pin to an external $10\text{-k}\Omega$ pull-up resistor to $\text{VCCPGM}$ . When you do not use as the dedicated $\text{CvP\_CONFDONE}$ optionally open-drain output, and when this pin is not used as an I/O pin, connect this pin as defined in the Intel Quartus Prime software. |

## **Differential I/O Pins**

Note:

Table 5. Differential I/O Pins

| Pin Name                                                                                | Pin<br>Functions      | Pin Description                                                                                                                                                                                                                                                                                                                                                                                | Connection Guidelines                                               |

|-----------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| LVDS[2,3] [A,B,C,D,E,F,G,H,I,J,K,L]_[1:24]p,LVDS[2,3] [A,B,C,D,E,F,G,H,I,J,K,L]_[1:24]n | I/O, TX/RX<br>channel | These are true LVDS receiver/transmitter channels on column I/O banks. Each I/O pair can be configured as LVDS receiver or LVDS transmitter. Pins with a "p" suffix carry the positive signal for the differential channel. Pins with an "n" suffix carry the negative signal for the differential channel. If not used for differential signaling, these pins are available as user I/O pins. | Connect unused pins as defined in the Intel Quartus Prime software. |

## **External Memory Interface and Hard Memory PHY Pins**

Note:

Table 6. External Memory Interface and Hard Memory PHY Pins

| Pin Name | Pin<br>Functions       | Pin Description                                                                                                                                                                                                                                                                                                                                                           | Connection Guidelines                                               |

|----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| DQS[#]   | I/O,bi-<br>directional | Optional data strobe signal for use in external memory interfacing. These pins drive to dedicated DQS phase shift circuitry.                                                                                                                                                                                                                                              | Connect unused pins as defined in the Intel Quartus Prime software. |

| DQSn[#]  | I/O,bi-<br>directional | Optional complementary data strobe signal for use in external memory interfacing. These pins drive to dedicated DQS phase shift circuitry.                                                                                                                                                                                                                                | Connect unused pins as defined in the Intel Quartus Prime software. |

| DQ[#]    | I/O,bi-<br>directional | Optional data signal for use in external memory interfacing. The order of the DQ bits within a designated DQ bus is not important. However, if you plan on migrating to a different memory interface that has a different DQ bus width, you will need to reevaluate your pin assignments. Analyze the available DQ pins across all pertinent DQS columns in the pin list. | Connect unused pins as defined in the Intel Quartus Prime software. |

| CQ[#]    | I/O, Input             | Optional data strobe signal for use in QDRII/II+/II+ Xtreme SRAM. These are the pins for echo clocks.                                                                                                                                                                                                                                                                     | Connect unused pins as defined in the Intel Quartus Prime software. |

|          | 1                      |                                                                                                                                                                                                                                                                                                                                                                           | continued                                                           |

| Pin Name              | Pin<br>Functions      | Pin Description                                                                                                                                                                                                                                                                                                                                                           | Connection Guidelines                                               |

|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| CQn[#]                | I/O, Input            | Optional complementary data strobe signal for use in QDRII/II+/II+ Xtreme SRAM. These are the pins for echo clocks.                                                                                                                                                                                                                                                       | Connect unused pins as defined in the Intel Quartus Prime software. |

| DQS[#]_[#]            | I/O,<br>bidirectional | Optional data strobe signal for use in external memory interfacing. These pins drive to dedicated DQS phase shift circuitry. The shifted DQS signal can also drive to internal logic.                                                                                                                                                                                     | Connect unused pins as defined in the Intel Quartus Prime software. |

| DQSn[#]_[#]           | I/O,<br>bidirectional | Optional complementary data strobe signal for use in external memory interfacing. These pins drive to dedicated DQS phase shift circuitry.                                                                                                                                                                                                                                | Connect unused pins as defined in the Intel Quartus Prime software. |

| DQ[#]_[#]_[#]         | I/O,<br>bidirectional | Optional data signal for use in external memory interfacing. The order of the DQ bits within a designated DQ bus is not important. However, if you plan on migrating to a different memory interface that has a different DQ bus width, you will need to reevaluate your pin assignments. Analyze the available DQ pins across all pertinent DQS columns in the pin list. | Connect unused pins as defined in the Intel Quartus Prime software. |

| CQ[#]_[#]/CQn[#]_[#]  | I/O, Input            | Optional data strobe signal for use in QDRII/II+/II+ Xtreme SRAM. These are the pins for echo clocks.                                                                                                                                                                                                                                                                     | Connect unused pins as defined in the Intel Quartus Prime software. |

| OK[#] <sup>[</sup> #] | I/O, Input            | Optional data strobe signal for use in RLDRAM 3.                                                                                                                                                                                                                                                                                                                          | Connect unused pins as defined in the Intel Quartus Prime software. |

| QKn[#]_[#]            | I/O, Input            | Optional complementary data strobe signal for use in RLDRAM 3.                                                                                                                                                                                                                                                                                                            | Connect unused pins as defined in the Intel Quartus Prime software. |

| DM[#]_[#]             | I/O, Output           | Optional write data mask, edge-aligned to DQ during write.                                                                                                                                                                                                                                                                                                                | Connect unused pins as defined in the Intel Quartus Prime software. |

| RESET_N_0             | I/O, Output           | Active low reset signal.                                                                                                                                                                                                                                                                                                                                                  | Connect unused pins as defined in the Intel Quartus Prime software. |

| A_[#]                 | I/O, Output           | Address input for DDR3, DDR4, QDRII/II+/II+ Xtreme SRAM, and RLDRAM3.                                                                                                                                                                                                                                                                                                     | Connect unused pins as defined in the Intel Quartus Prime software. |

| BA_[#]                | I/O, Output           | Bank address input for DDR2, DDR3, and RLDRAM 3.                                                                                                                                                                                                                                                                                                                          | Connect unused pins as defined in the Intel Quartus Prime software. |

| CK_[#]                | I/O, Output           | Input clock for external memory devices.                                                                                                                                                                                                                                                                                                                                  | Connect unused pins as defined in the Intel Quartus Prime software. |

|                       |                       |                                                                                                                                                                                                                                                                                                                                                                           | continued                                                           |

#### PCG-01017 | 2018.03.30

| CK_N_[#]  CKE_[#]  CS_N_[#]  REF# | I/O, Output  I/O, Output  I/O, Output  I/O, Output | Input clock for external memory devices, inverted CK.  High signal enables clock, low signal disables clock.  Active low chip select.                                                                                                                                                                                                                        | Connect unused pins as defined in the Intel Quartus Prime software.  Connect unused pins as defined in the Intel Quartus Prime software.                                                                                                                                                                                                     |

|-----------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS_N_[#]                          | I/O, Output                                        |                                                                                                                                                                                                                                                                                                                                                              | software.                                                                                                                                                                                                                                                                                                                                    |

|                                   |                                                    | Active low chip select.                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                              |

| REF#                              | I/O, Output                                        |                                                                                                                                                                                                                                                                                                                                                              | Connect unused pins as defined in the Intel Quartus Prime software.                                                                                                                                                                                                                                                                          |

|                                   |                                                    | Auto-refresh control input for RLDRAM 3.                                                                                                                                                                                                                                                                                                                     | Connect unused pins as defined in the Intel Quartus Prime software.                                                                                                                                                                                                                                                                          |

| ODT_[#]                           | I/O, Output                                        | On die termination signal to set the termination resistors to each pin.                                                                                                                                                                                                                                                                                      | Connect unused pins as defined in the Intel Quartus Prime software.                                                                                                                                                                                                                                                                          |

| WE_N_0                            | I/O, Output                                        | Write-enable input for DDR3 SDRAM, RLDRAM 3, and all supported protocols.                                                                                                                                                                                                                                                                                    | Connect unused pins as defined in the Intel Quartus Prime software.                                                                                                                                                                                                                                                                          |