## Gowin FPGA Products

## **Programming and Configuration Guide**

UG290-2.6.7E, 03/13/2023

Copyright © 2023 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

GOWIN, Gowin, LittleBee, and GOWINSEMI are trademarks of Guangdong Gowin Semiconductor Corporation and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

## **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                                                                                                                                     |

|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4/17/2017  | 1.00E   | Initial version published.                                                                                                                                                                                                                                                                                                                                                      |

| 5/31/2017  | 1.01E   | <ul> <li>Configuration mode and value of different supported device updated.</li> <li>RECONFIG N notes during programming built-in Flash updated.</li> </ul>                                                                                                                                                                                                                    |

| 10/13/2017 | 1.02E   | Description of reusing pins updated.                                                                                                                                                                                                                                                                                                                                            |

| 3/16/2018  | 1.03E   | GW1NS programming and configuration description added.                                                                                                                                                                                                                                                                                                                          |

| 8/8/2018   | 1.04E   | <ul> <li>The description of configuration process when Flash is empty updated.</li> <li>Operation procedures for multiple configurations updated.</li> <li>When MODE[0]=1, JTAG pins reuse description updated.</li> <li>The programming features of B version devices updated.</li> <li>Configuration notes and the timing for different configuration modes added.</li> </ul> |

| 1/8/2019   | 1.05E   | <ul> <li>The configuration timing and parameters for SERIAL mode added.</li> <li>The description of power supply requirements deleted.</li> </ul>                                                                                                                                                                                                                               |

| 8/16/2019  | 1.06E   | <ul> <li>Power up description and configuration flow added.</li> <li>The description of File Size Configuration modified.</li> </ul>                                                                                                                                                                                                                                            |

| 5/15/2020  | 2.0E    | <ul> <li>The note of JTAGSEL_N used as IO added.</li> <li>GW1N(RS/GW1N(R)-2B/GW1N(R)-6 removed.</li> <li>Configuration mode description optimized.</li> </ul>                                                                                                                                                                                                                   |

| 8/20/2020  | 2.1E    | <ul><li>JTAG Configuration added.</li><li>SSPI Configuration added.</li><li>AES Programming added.</li></ul>                                                                                                                                                                                                                                                                    |

| 10/30/2020 | 2.2E    | Configuration File Loading Time added.                                                                                                                                                                                                                                                                                                                                          |

| 02/07/2021 | 2.3E    | I <sup>2</sup> C Configuration added.                                                                                                                                                                                                                                                                                                                                           |

| 09/24/2021 | 2.4E    | <ul> <li>Configuration process added.</li> <li>The flow chart of configuring or programming SRAM/Flash for GW1N-2 added.</li> <li>Process of internal Flash programming added.</li> </ul>                                                                                                                                                                                       |

| 01/20/2022 | 2.4.1E  | Remarks about I <sup>2</sup> C configuration mode added.                                                                                                                                                                                                                                                                                                                        |

| 05/07/2022 | 2.5E    | <ul><li>Information on GW2AN-9X/18X deleted.</li><li>6.5 MSPI section updated.</li></ul>                                                                                                                                                                                                                                                                                        |

| 05/10/2022 | 2.5.1E  | CPU Mode Configuration Timing diagram updated.                                                                                                                                                                                                                                                                                                                                  |

| 07/14/2022 | 2.5.2E  | <ul> <li>Information on configuration file size added.</li> <li>Count of address and length of one address of GW1N-2 SRAM updated.</li> <li>Description of loading frequency for GW1N-2 devices added.</li> </ul>                                                                                                                                                               |

| 08/10/2022 | 2.5.3E  | <ul> <li>Table 6-6 Gowin FPGA ID CODE updated.</li> <li>Table 6-9 TCK Frequency Requirements for JTAG updated.</li> </ul>                                                                                                                                                                                                                                                       |

| 09/07/2022 | 2.5.4E  | <ul> <li>The note on I<sup>2</sup>C configuration mode updated.</li> <li>The description of READY pin and DONE pin in Table 5-3 Pin Function added.</li> <li>Table 6 5 Gowin FPGA ID CODE updated.</li> </ul>                                                                                                                                                                   |

| 10/28/2022 | 2.6E    | <ul> <li>Information on GW1NS-2/2C, GW1NSR-2/2C, and GW1NSE-2C removed.</li> <li>Information on GW1N-1P5 updated.</li> <li>Description of CLKHOLD_N pin updated.</li> </ul>                                                                                                                                                                                                     |

| 11/11/2022 | 2.6.1E  | Section "6.4.5 Connection Diagram for SSPI Configuration                                                                                                                                                                                                                                                                                                                        |

| Date       | Version | Description                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |         | <ul> <li>Mode" updated.</li> <li>Section "Programming External Flash or Embedded SPI-Flash" updated.</li> <li>Section "Read Status Register 0x41" updated.</li> <li>Description of the multiplexing of JTAG pins and JTAGSEL_N pin added.</li> <li>Figure 7-7 Program AES Key Flow updated.</li> <li>FPGA erasure process of T Technology updated.</li> </ul> |

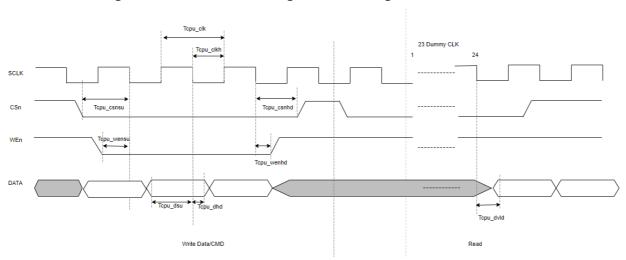

| 11/24/2022 | 2.6.2E  | <ul> <li>Table 6-18 CPU Mode Pins updated.</li> <li>Table 6-19 CPU Configuration Timing Parameters added.</li> <li>Figure 6-60 CPU Mode Configuration diagram updated.</li> <li>Figure 6-61 CPU Mode Configuration Timing added.</li> </ul>                                                                                                                   |

| 12/02/2022 | 2.6.3E  | <ul> <li>Description of the background upgrade feature in section 6.1<br/>Configuration Notes updated.</li> </ul>                                                                                                                                                                                                                                             |

| 01/12/2023 | 2.6.4E  | <ul> <li>Note added to Table 6-22 Pin Definition in I2C Configuration Mode.</li> <li>Table 7-3 Loading Time in MSPI Mode updated.</li> <li>Table 7-4 Loading Time in Autoboot Mode updated.</li> <li>Table 10-1 SPI Flash Commands updated.</li> </ul>                                                                                                        |

| 01/20/2023 | 2.6.5E  | <ul> <li>Note added to Table 10-1 SPI Flash Commands.</li> <li>Figure 6-60 CPU Mode Configuration diagram updated.</li> <li>Figure 6-61 CPU Mode Configuration Timing updated.</li> </ul>                                                                                                                                                                     |

| 02/02/2023 | 2.6.6E  | <ul> <li>Table 6-19 CPU Configuration Timing Parameters updated.</li> <li>Note under Table 10-1 SPI Flash Commands modified.</li> </ul>                                                                                                                                                                                                                       |

| 02/13/2023 | 2.6.7E  | Note about programming internal Flash using I <sup>2</sup> C added.                                                                                                                                                                                                                                                                                           |

## **Contents**

|   | Contents                                                 |     |

|---|----------------------------------------------------------|-----|

| L | ist of Figures                                           | iii |

| L | ist of Tables                                            | vi  |

| 1 | About This Guide                                         | 1   |

|   | 1.1 Purpose                                              | 1   |

|   | 1.2 Related Documents                                    | 1   |

|   | 1.3 Terminology and Abbreviations                        | 2   |

|   | 1.4 Support and Feedback                                 | 2   |

| 2 | 2 Glossary                                               | 3   |

| 3 | Configuration Modes                                      | 5   |

|   | 3.1 LittleBee® Family of FPGA Products                   | 5   |

|   | 3.2 Arora Family of FPGA Products                        | 7   |

| 4 | Configuration Process                                    | 8   |

|   | 4.1 Power-up Sequence                                    | 10  |

|   | 4.2 Initialization                                       | 11  |

|   | 4.3 Configuration                                        | 11  |

|   | 4.4 Wake-up                                              | 11  |

|   | 4.5 User Mode                                            | 12  |

| 5 | Configuration Pins                                       | 13  |

|   | 5.1 Configuration Pin List and Reuse Options             | 13  |

|   | 5.1.1 Configuration Pin List                             | 13  |

|   | 5.1.2 Configuration Pin Reuse                            |     |

|   | 5.2 Configuration Pin Function and Application           | 16  |

| 6 | Configuration Mode Introduction                          | 21  |

|   | 6.1 Configuration Notes                                  | 21  |

|   | 6.2 JTAG Configuration                                   | 25  |

|   | 6.2.1 JTAG Configuration Mode Pins                       |     |

|   | 6.2.2 Connection Diagram for the JTAG Configuration Mode |     |

|   | 6.2.3 JTAG Configuration Timing                          |     |

|   | 6.2.4 JTAG Configuration Process                         | 29  |

| 6.3 AUTO BOOT Configuration (Supported by LittleBee® Family Only)  |     |

|--------------------------------------------------------------------|-----|

| 6.4 SSPI                                                           |     |

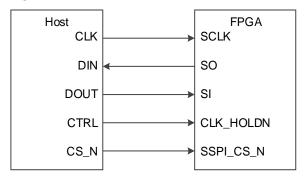

| 6.4.1 SSPI Mode Pins                                               |     |

| 6.4.2 SSPI Configuration Timing                                    |     |

| 6.4.3 Configuration Instruction                                    |     |

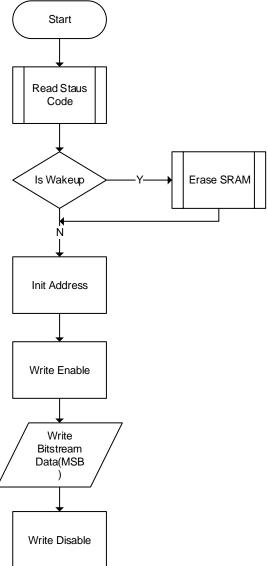

| 6.4.4 The Flow Chart of Configuring SRAM via SSPI                  |     |

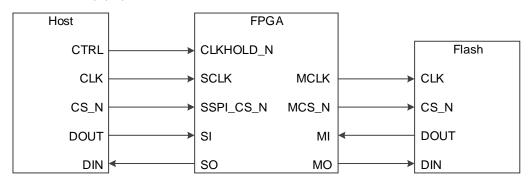

| 6.4.5 Connection Diagram for SSPI Configuration Mode               |     |

| 6.4.6 Multiple FPGA Connection View in SSPI Mode                   |     |

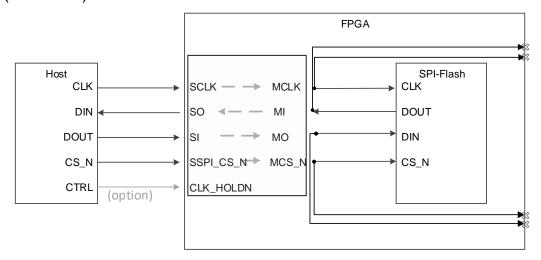

| 6.5 MSPI                                                           |     |

| 6.5.1 MSPI Mode Pins                                               |     |

| 6.5.2 Connection Diagram for MSPI Configuration Mode               |     |

| 6.5.3 MSPI Mode Configuration Attempts                             |     |

| 6.5.4 MULTI BOOT                                                   |     |

| 6.5.5 MSPI Configuration Timing                                    |     |

| 6.6 DUAL BOOT Configuration (Supported by LittleBee® Family Only)  |     |

| 6.7 CPU Mode                                                       |     |

| 6.7.1 Configuration Timing                                         |     |

| 6.8 SERIAL Mode                                                    |     |

| 6.9 I <sup>2</sup> C Mode                                          |     |

| 6.9.1 Process of GW1N-2 Configuring or Programming SRAM/Flash      | 92  |

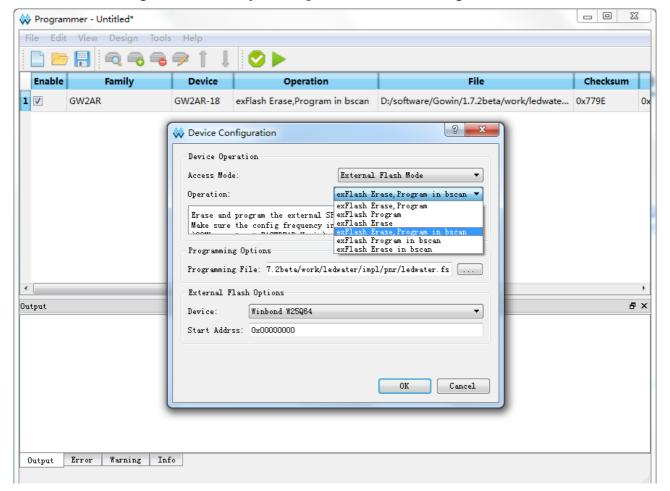

| 7 Bitstream File Configuration                                     | 93  |

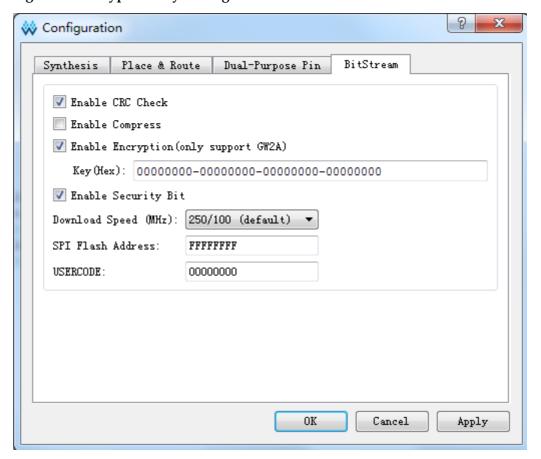

| 7.1 Configuration Options                                          | 93  |

| 7.2 Configuration Data Encryption (Supported by Arora Family only) | 94  |

| 7.2.1 Definition                                                   | 94  |

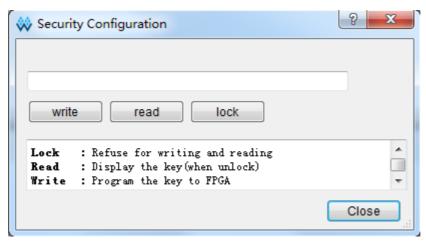

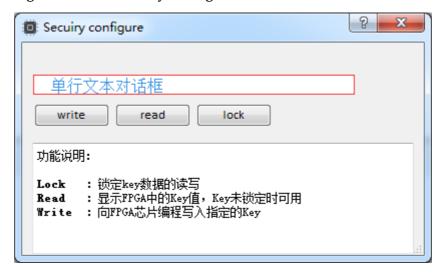

| 7.2.2 Enter Encryption KEY                                         | 95  |

| 7.2.3 Enter the Decrypt Key                                        | 95  |

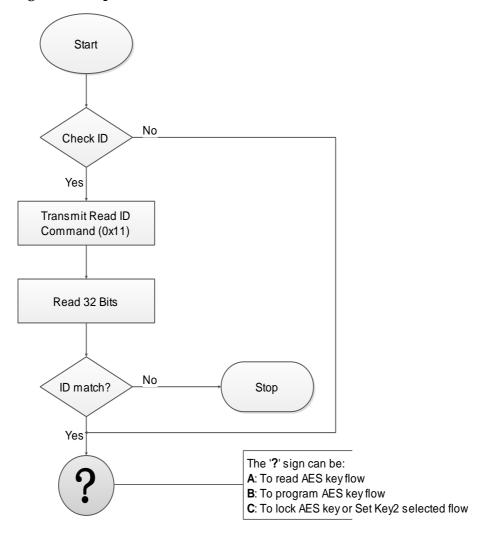

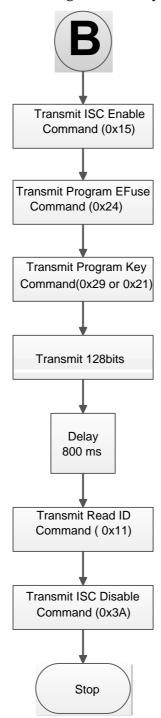

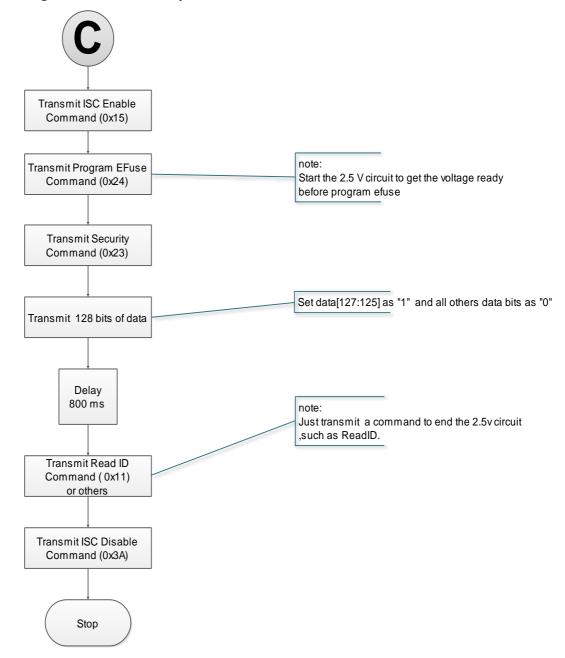

| 7.2.4 Programming Operation                                        | 96  |

| 7.2.5 Programming Flow                                             | 98  |

| 7.3 Configuration File Size                                        | 101 |

| 7.4 Configuration File Loading Time                                | 103 |

| 8 Safety Precautions                                               | 106 |

| 9 Boundary Scan                                                    | 108 |

| 10 SPI Flash Selection                                             | 110 |

## **List of Figures**

| Figure 4-1 Configuration Flow                                                                          | 9  |

|--------------------------------------------------------------------------------------------------------|----|

| Figure 4-2 POR Power-up Timing                                                                         | 10 |

| Figure 5-1 Configuring Pin Reuse                                                                       | 16 |

| Figure 5-2 MCLK Frequency Setting                                                                      | 19 |

| Figure 6-1 Recommended Pin Connection                                                                  | 23 |

| Figure 6-2 Power Recycle Timing                                                                        | 24 |

| Figure 6-3 Trigger Timing                                                                              | 24 |

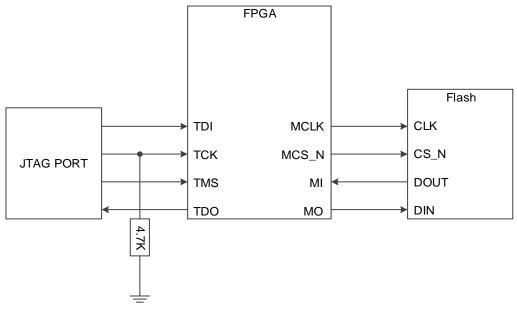

| Figure 6-4 Connection Diagram for JTAG Configuration Mode                                              | 27 |

| Figure 6-5 Connection Diagram of JTAG Daisy-Chain Configuration Mode                                   | 28 |

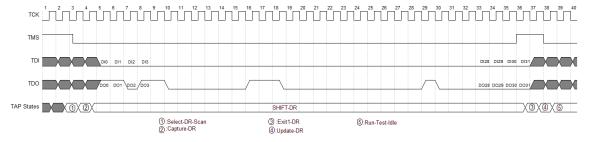

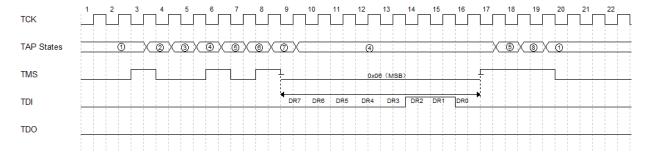

| Figure 6-6 JTAG Configuration timing                                                                   | 28 |

| Figure 6-7 TAP State Machine                                                                           | 29 |

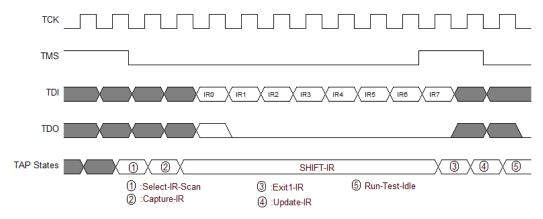

| Figure 6-8 Instruction Register Access Timing                                                          | 30 |

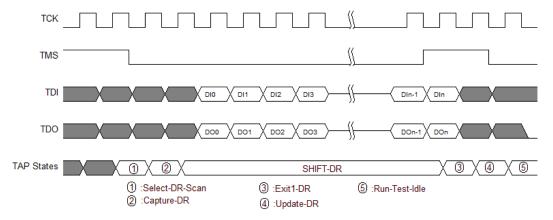

| Figure 6-9 Data Register Access Timing                                                                 | 30 |

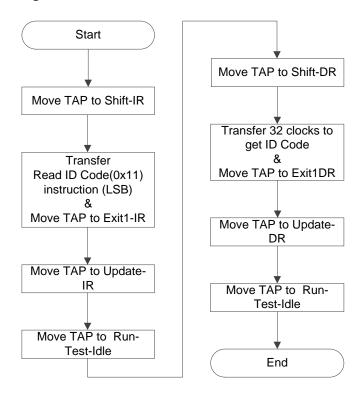

| Figure 6-10 Read Machine Flow Chart in ID Code State                                                   | 32 |

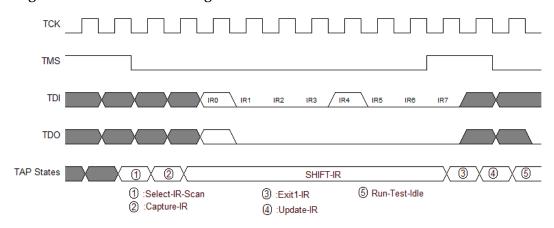

| Figure 6-11 The Access Timing of Read ID Code Instruction- 0x11                                        | 32 |

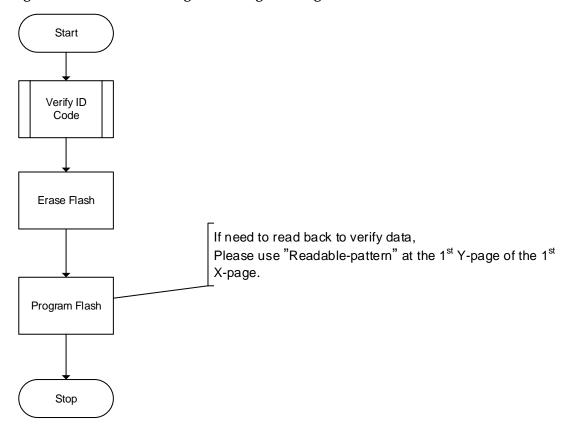

| Figure 6-12 Read ID Code Data Register Access Timing                                                   | 32 |

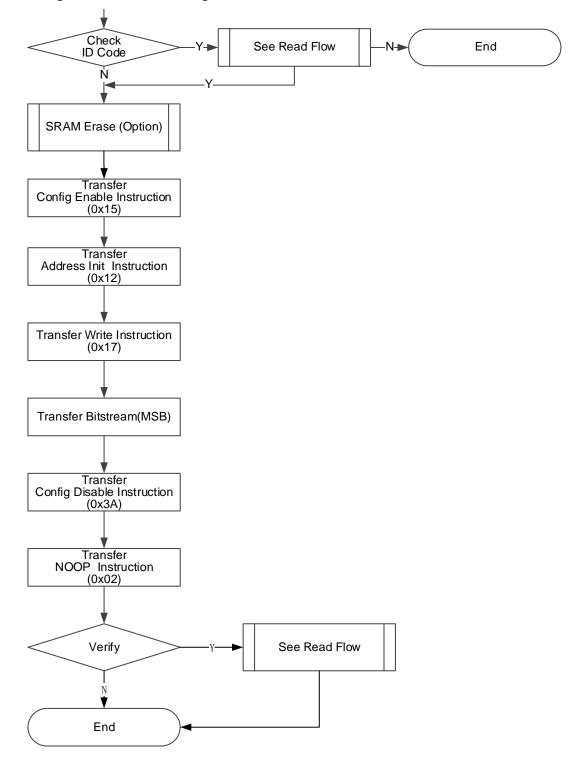

| Figure 6-13 SRAM Configuration Flow                                                                    | 34 |

| Figure 6-14 Process of reading SRAM                                                                    | 36 |

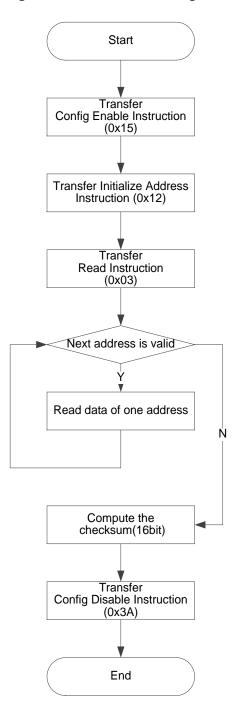

| Figure 6-15 Process of Normal Programming                                                              | 38 |

| Figure 6-16 Process of Background Programming                                                          | 39 |

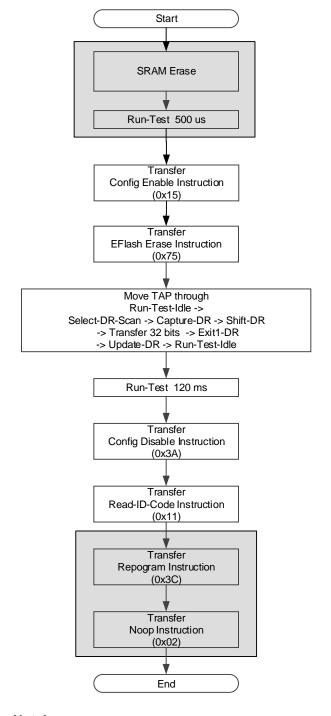

| Figure 6-17 The Embedded Flash Erasing process of T Technology                                         | 41 |

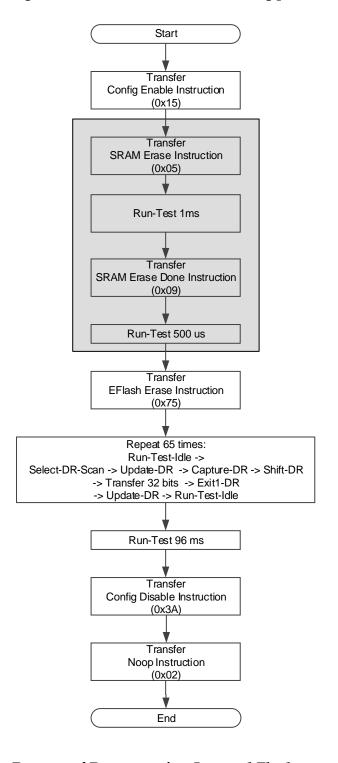

| Figure 6-18 The Embedded Flash Erasing process of H Technology                                         | 43 |

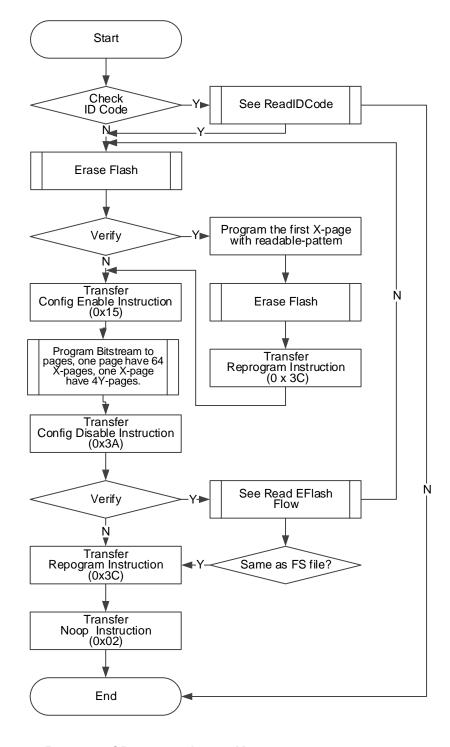

| Figure 6-19 Process of Programming Internal Flash View                                                 | 45 |

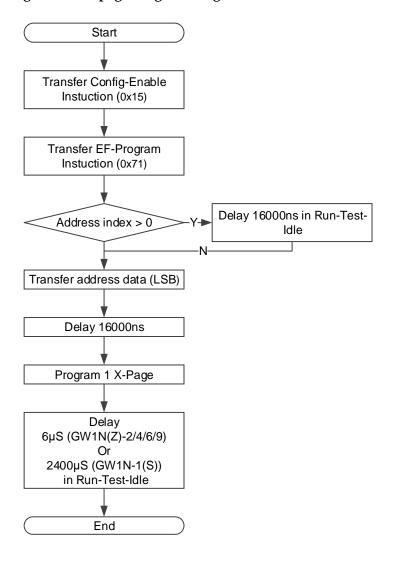

| Figure 6-20 X-page Programming                                                                         | 46 |

| Figure 6-21 Y-page Programming                                                                         | 47 |

| Figure 6-22 Process of Reading Internal Flash                                                          | 48 |

| Figure 6-23 Process of Reading a Y-page                                                                | 49 |

| Figure 6-24 GW1N-4 Background Programming Flow                                                         | 50 |

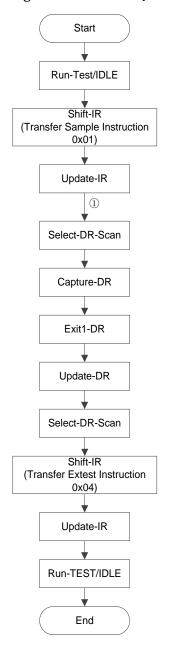

| Figure 6-25 Transfer JTAG Instruction Sample & Extest Flow Chart                                       | 51 |

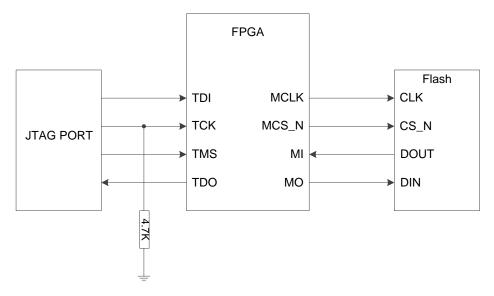

| Figure 6-26 Connection Diagram of Programming External Flash via JTAG Interface(GW2A-18/GW2A-55 /GW1N) | 51 |

UG290-2.6.7E iii

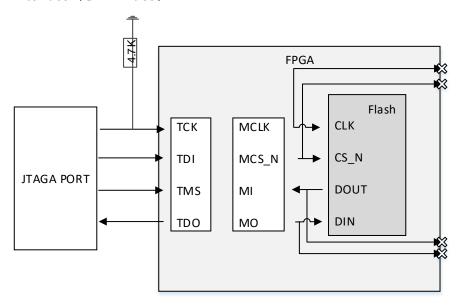

| Figure6-27 Connection Diagram of Programming Embedded SPI Flash via JTAG Interface 55)   |    |

|------------------------------------------------------------------------------------------|----|

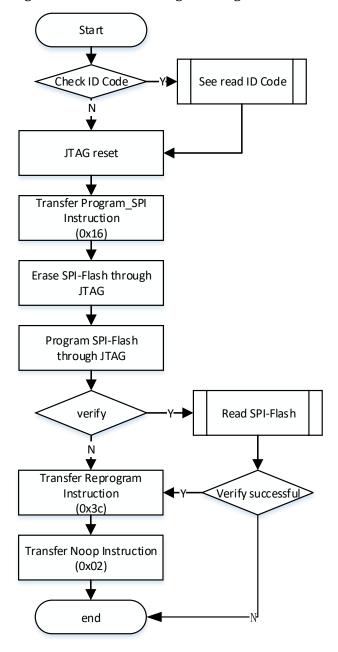

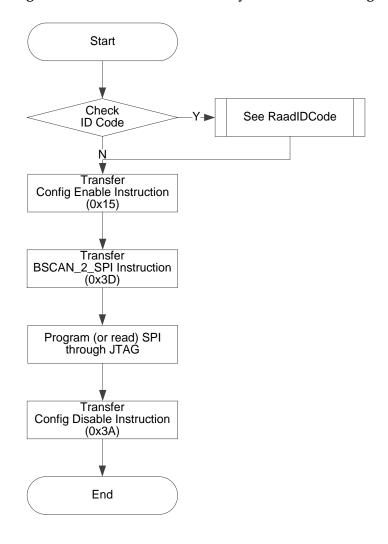

| Figure 6-28 Process of Programming SPI Flash                                             | 53 |

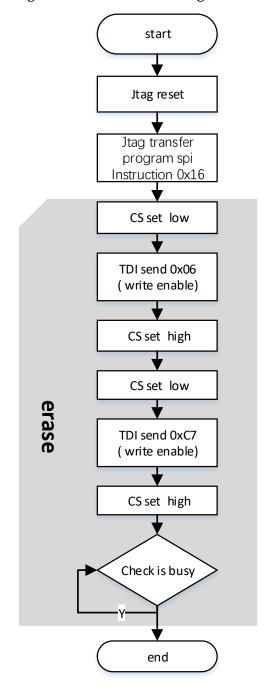

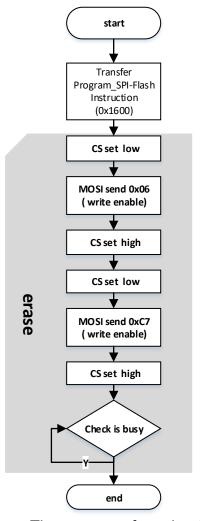

| Figure 6-29 Process of Erasing SPI Flash                                                 | 54 |

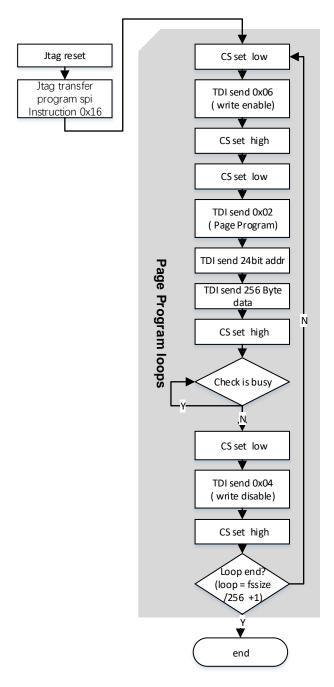

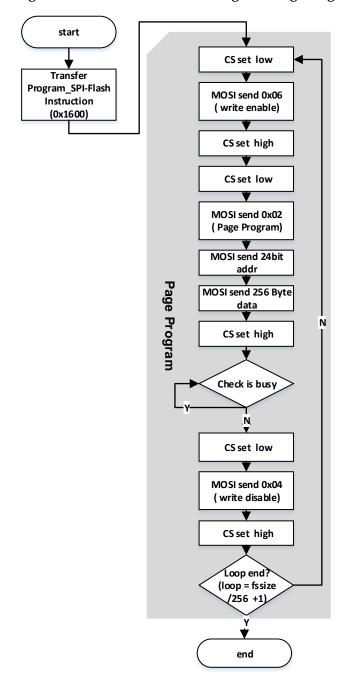

| Figure 6-30 Process of Programming a Page of the SPI Flash                               | 55 |

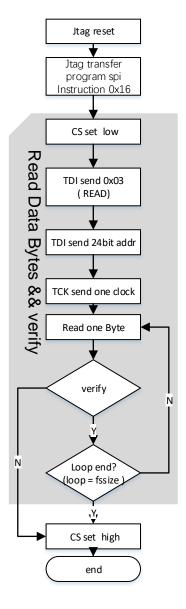

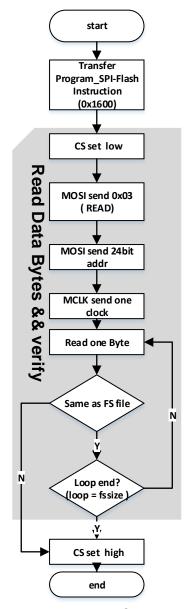

| Figure 6-31 Process of Reading Back SPI Flash and Verifying the Data Stream File         | 56 |

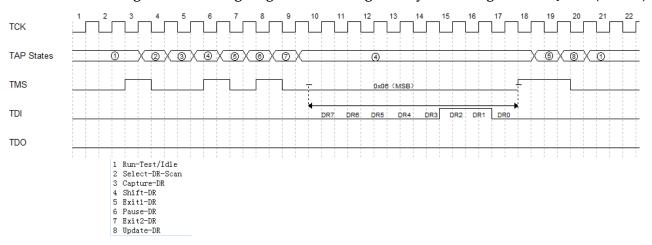

| Figure 6-32 Timing diagram of Sending 0x06 by Emulating SPI with JTAG(GW2A)              | 57 |

| Figure 6-33 Timing diagram of Sending 0x06 by Emulating SPI with JTAG(GW1N)              | 57 |

| Figure 6-34 Process of Use Boundary Scan Mode To Program SPI Flash                       | 58 |

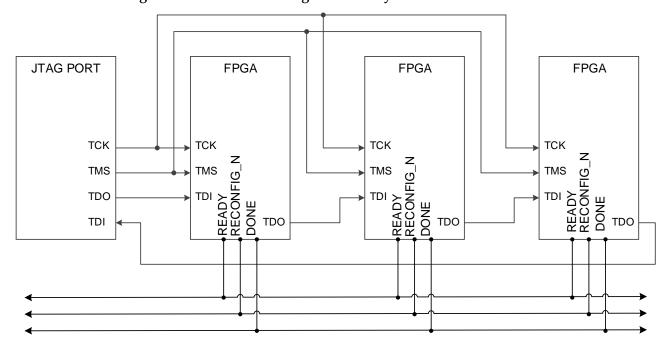

| Figure 6-35 Connection Diagram of Daisy-Chain                                            | 61 |

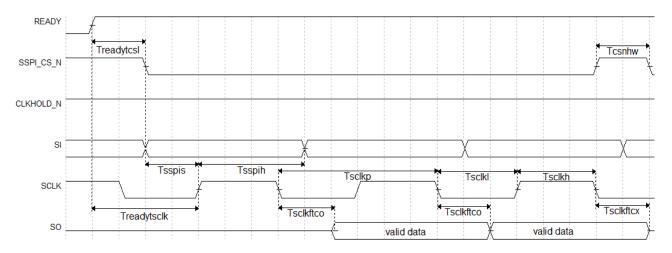

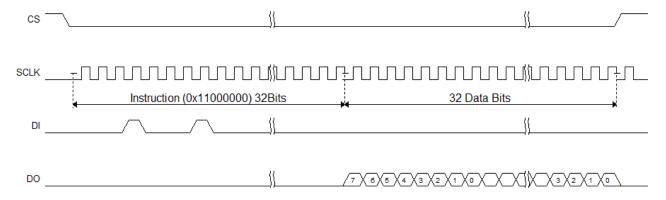

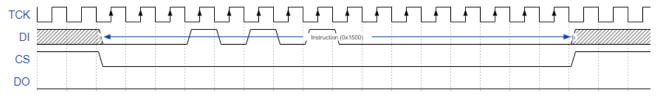

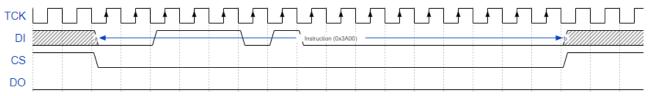

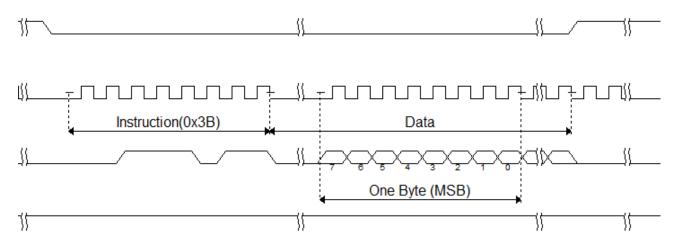

| Figure 6-36 SSPI Configuration Timing                                                    | 63 |

| Figure 6-37 Read ID Code Timing                                                          | 64 |

| Figure 6-38 Write Enable (0x15) Timing                                                   | 65 |

| Figure 6-39 Write Disable(0x3A00) Timing                                                 | 65 |

| Figure 6-40 Write Data (0x3B) Timing                                                     | 66 |

| Figure 6-41 SSPI Configuration Mode Connection Diagram                                   | 67 |

| Figure 6-42 Connection Diagram of Programming External Flash via SSPI(GW2A-18/55,GV      |    |

| Figure 6-43 Connection Diagram of Programming Internal Flash via SSPI (GW2AN-55)         | 68 |

| Figure 6-44 The Flow Chart of Programming Flash via SSPI                                 | 69 |

| Figure 6-45 The Flow Chart of Erasing SPI Flash                                          | 70 |

| Figure 6-46 The Flow Chart of Programming a Page of the SPI Flash                        | 71 |

| Figure 6-47 The Flow Chart of Reading Back SPI Flash and Verifying the Data Stream File. | 72 |

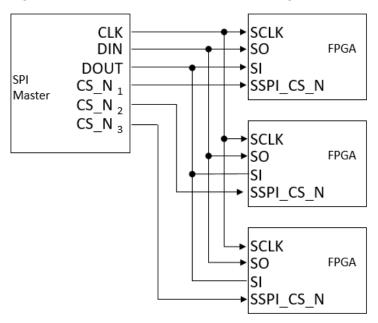

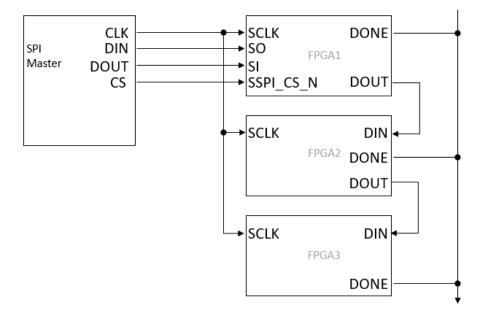

| Figure 6-48 Multiple FPGA Connection Diagram 1                                           | 73 |

| Figure 6-49 Multiple FPGA Connection Diagram 2                                           | 73 |

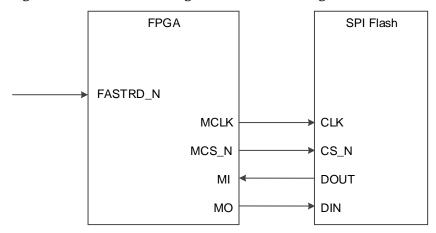

| Figure 6-50 Connection Diagram for MSPI Configuration Mode                               | 76 |

| Figure 6-51 Connection Diagram of JTAG Programming External Flash                        | 76 |

| Figure 6-52 Example of Bitstream Image Distribution in Flash Memory                      | 78 |

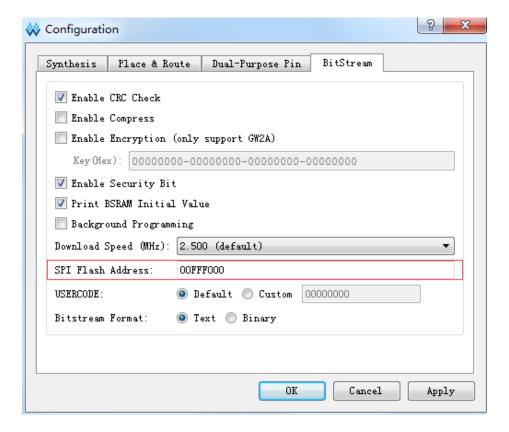

| Figure 6-53 Input the Start address for the Next Bitstream                               | 79 |

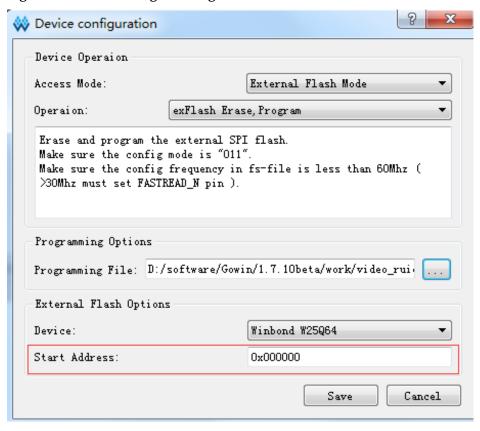

| Figure 6-54 Set the Programming Address for the External Flash                           | 80 |

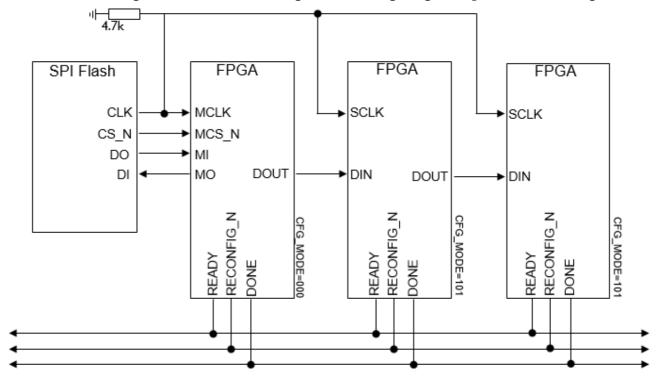

| Figure 6-55 Connection Diagram for Configuring Multiple FPGAs via Single Flash           | 81 |

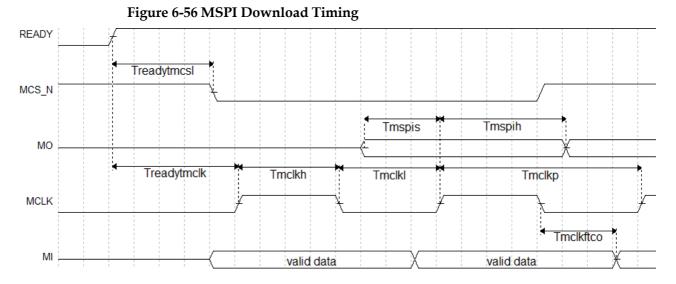

| Figure 6-56 MSPI Download Timing                                                         | 81 |

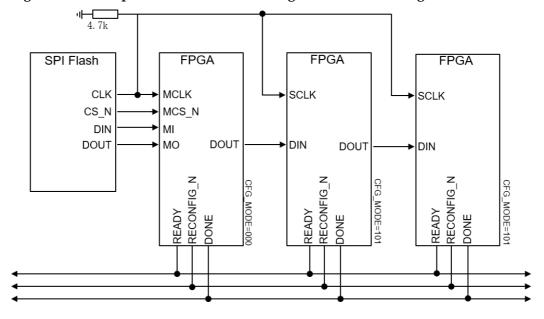

| Figure 6-57 Multiple FPGA Connection Diagram in MSPI Configuration Mode                  | 82 |

| Figure 6-58 Dual Boot Flow Chart                                                         | 83 |

| Figure 6-59 Connection Diagram for CPU Mode                                              | 85 |

| Figure 6-60 CPU Mode Configuration diagram                                               | 85 |

| Figure 6-61 CPU Mode Configuration Timing                                                | 86 |

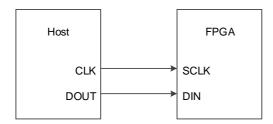

| Figure 6-62 Connection Diagram for SERIAL Mode                                           | 87 |

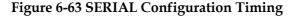

| Figure 6-63 SERIAL Configuration Timing                                                  | 88 |

| Figure 6-64 Connection Diagram for I <sup>2</sup> C Mode                                 | 89 |

UG290-2.6.7E iv

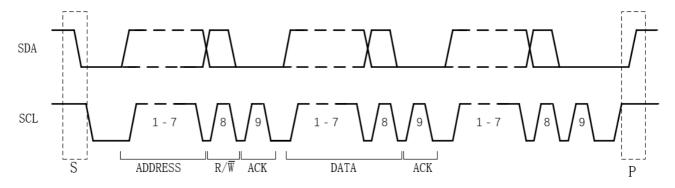

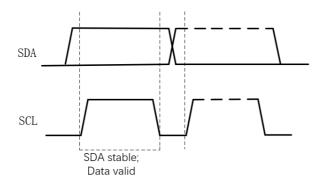

| Figure 6-65 I <sup>2</sup> C Mode Timing                            | 89  |

|---------------------------------------------------------------------|-----|

| Figure 6-66 Process of GW1N-2 Configuring or Programming SRAM/Flash | 92  |

| Figure 7-1 Configuration Options                                    | 94  |

| Figure 7-2 Encryption Key Setting Method                            | 95  |

| Figure 7-3 Setting the Decryption Key                               | 96  |

| Figure 7-4 AES Security Configure                                   | 97  |

| Figure 7-5 Prepare                                                  | 98  |

| Figure 7-6 Read AES Key Flow                                        | 99  |

| Figure 7-7 Program AES Key Flow                                     | 100 |

| Figure 7-8 Lock AES Key Flow                                        | 101 |

| Figure 7-9 Bitstream Format generation                              | 102 |

| Figure 9-1 Boundary Scan Operation Schematic Diagram                | 109 |

UG290-2.6.7E

## **List of Tables**

| Table 1-1 Abbreviations and Terminology                                                  | 2  |

|------------------------------------------------------------------------------------------|----|

| Table 2-1 Glossary                                                                       | 3  |

| Table 3-1 Configuration Modes                                                            | 6  |

| Table 3-2 Configuration Modes                                                            | 7  |

| Table 4-1 Power Rails Monitored by POR Circuits of Different Devices                     | 10 |

| Table 5-1 Configuration Pin List                                                         | 13 |

| Table 5-2 Pin Reuse Options                                                              | 15 |

| Table 5-3 Pin Function                                                                   | 16 |

| Table 6-1 Timing Parameters for Cycling Power and RECONFIG_N Trigger                     | 24 |

| Table 6-2 Timing Parameters for Power-on again and RECONFIG_N Triggering (Arora Family)  | 25 |

| Table 6-3 Pin Description in JTAG Configuration Mode                                     | 25 |

| Table 6-4 List of devices for which you need/do not need to send a reprogram instruction | 26 |

| Table 6-5 JTAG Configuration Timing Parameters                                           | 28 |

| Table 6-6 Gowin FPGA ID CODE                                                             | 31 |

| Table 6-7 Change of TDI and TMS Value in The Process of Sending Instructions             | 31 |

| Table 6-8 Count of Address and Length of One Address                                     | 35 |

| Table 6-9 TCK Frequency Requirements for JTAG                                            | 39 |

| Table 6-10 Readback-pattern / Autoboot-pattern                                           | 44 |

| Table 6-11 Pin State                                                                     | 58 |

| Table 6-12 Status Register Definition                                                    | 59 |

| Table 6-13 SSPI Mode Pins                                                                | 62 |

| Table 6-14 SSPI Configuration Timing Parameters                                          | 63 |

| Table 6-15 Configuration Instruction                                                     | 64 |

| Table 6-16 Pin Description in MSPI Configuration Mode                                    | 75 |

| Table 6-17 MSPI Configuration Timing Parameters                                          | 82 |

| Table 6-18 CPU Mode Pins                                                                 | 84 |

| Table 6-19 CPU Configuration Timing Parameters                                           | 86 |

| Table 6-20 Pin Definition in SERIAL Configuration Mode                                   | 87 |

| Table 6-21 SERIAL Configuration Timing Parameters                                        | 88 |

| Table 6-22 Pin Definition in I <sup>2</sup> C Configuration Mode                         | 89 |

| Table 6-23 I <sup>2</sup> C Configuration Timing Parameters                              | 90 |

| Table 6-24 Frequencies and addresses of I <sup>2</sup> C configuration mode | 91  |

|-----------------------------------------------------------------------------|-----|

| Table 7-1 Gowin FPGA Products Configuration File Size (Max.)                | 102 |

| Table 7-2 Loading Frequency of Config File                                  | 103 |

| Table 7-3 Loading Time in MSPI Mode                                         | 105 |

| Table 7-4 Loading Time in Autoboot Mode                                     | 105 |

| Table 10-1 SPI Flash Commands                                               | 110 |

UG290-2.6.7E vii

1 About This Guide 1.1 Purpose

## 1 About This Guide

## 1.1 Purpose

This guide mainly introduces general features and functions on programming and configuration of LittleBee® family devices and Arora family devices. It helps users to use Gowin FPGA products to their full potential.

## 1.2 Related Documents

The latest user guides are available on the GOWINSEMI Website.

You can find the related documents at www.gowinsemi.com:

- DS100, GW1N series of FPGA Products Data Sheet

- DS102, GW2A series of FPGA Products Data Sheet

- DS117, GW1NR series of FPGA Products Data Sheet

- DS226, GW2AR series of FPGA Products Data Sheet

- DS961, GW2ANR series of FPGA Products Data Sheet

- DS821, GW1NS series of FPGA Products Data Sheet

- DS841, GW1NZ series of FPGA Products Data Sheet

- DS861, <u>GW1NSR series of FPGA Products Data Sheet</u>

- DS871, <u>GW1NSE series of FPGA Products Data Sheet</u>

- DS881, GW1NSER series of FPGA Products Data Sheet

- DS891, GW1NRF series of FPGA Products Data Sheet

- DS961, GW2ANR series of FPGA Products Data Sheet

- DS976, <u>GW2AN-55 Data Sheet</u>

UG290-2.6.7E 1(110)

## 1.3 Terminology and Abbreviations

The terminology and abbreviations used in this manual are as shown in Table 1-1.

Table 1-1 Abbreviations and Terminology

| Terminology and Abbreviations | Full Name                                         |

|-------------------------------|---------------------------------------------------|

| Bitstream                     | Bitstream Data                                    |

| Bscan                         | Boundary Scan                                     |

| CPU                           | Central Processing Unit                           |

| CRC                           | Cyclic Redundancy Check                           |

| EFlash/EmbFlash               | Embedded Flash                                    |

| FPGA                          | Field Programmable Gate Array                     |

| FS file                       | Fuses file                                        |

| GPIO                          | General Purpose Input Output                      |

| I2C (I <sup>2</sup> C、IIC)    | Inter-Integrated Circuits                         |

| ID                            | Identification                                    |

| IEEE                          | Institute of Electrical and Electronics Engineers |

| Internal Flash                | Internal Flash                                    |

| JTAG                          | Joint Test Action Group                           |

| LSB                           | Least Significant Bit                             |

| LUT                           | Look-up Table                                     |

| MSB                           | Most Significant Bit                              |

| MSPI                          | Master Serial Peripheral Interface                |

| Programming                   | Programming                                       |

| SCL                           | Serial Clock                                      |

| SDA                           | Serial Data                                       |

| Security Bit                  | Security Bit                                      |

| SPI                           | Serial Peripheral Interface                       |

| SRAM                          | Static Random Access Memory                       |

| SSPI                          | Slave Serial Peripheral Interface                 |

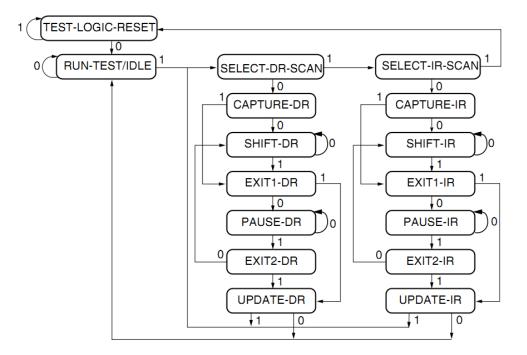

| TAP                           | Test Access Port                                  |

## 1.4 Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: <a href="www.gowinsemi.com">www.gowinsemi.com</a></a> E-mail:<a href="mail:support@gowinsemi.com">support@gowinsemi.com</a></a>

UG290-2.6.7E 2(110)

## **2**Glossary

This chapter presents an overview of the terms that are commonly used in the process of programming and configuring Gowin FPGA products to help users get familiar with the related concepts.

Table 2-1 Glossary

| Glossary                   | Meaning                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program                    | Write the bitstream data generated by Gowin Software to the embedded Flash or external SPI Flash of FPGA.                                                                                                                                                                                                                                                         |

| Configure                  | Load the bitstream data generated by Gowin Software to the FPGA SRAM via external interfaces or embedded Flash.                                                                                                                                                                                                                                                   |

| GowinCONFIG                | In addition to the generic JTAG configuration mode, Gowin FPGA products support additional configurations, including AUTO BOOT configuration, DUAL BOOT configuration, MSPI configuration, SSPI configuration, SERIAL configuration, and CPU configuration. How many GowinCONFIG configuration modes each device supports depend on the device model and package. |

| MODE[2:0]                  | A representation of the three MODE pin values associated with GowinCONFIG.                                                                                                                                                                                                                                                                                        |

| AUTO BOOT<br>Configuration | FPGA loads bitstream data into the SRAM from an embedded Flash. Only non-volatile devices support this mode.                                                                                                                                                                                                                                                      |

| DUAL BOOT<br>Configuration | Two bitstream files are stored in embedded Flash and external Flash separately. Switch to the embedded Flash if the external Flash fails to configure. Only non-volatile devices support this mode.                                                                                                                                                               |

| MSPI Configuration         | As a master, FPGA is configured by reading bitstream from the external Flash via the SPI interface automatically.                                                                                                                                                                                                                                                 |

| SSPI Configuration         | As a slave device, the bitstream data is written into the FPGA via the SPI interface by the external master.                                                                                                                                                                                                                                                      |

| SERIAL Configuration       | As a slave device, the bitstream data is written into the FPGA via the serial interface by the external master.                                                                                                                                                                                                                                                   |

UG290-2.6.7E 3(110)

| Glossary                       | Meaning                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

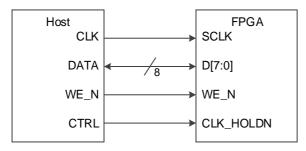

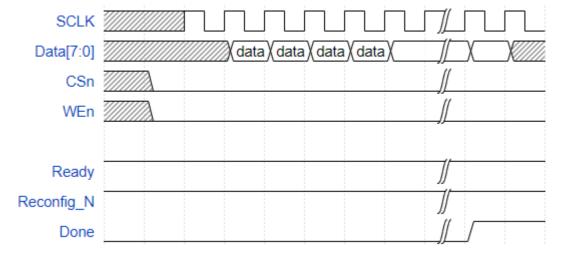

| CPU Configuration              | As a slave device, the bitstream data is written into the FPGA via the parallel interface (8-bit) by the external master.                                                                                                                                                                                                                                                                                         |

| I <sup>2</sup> C Configuration | As a slave device, the bitstream data is written into the FPGA via the I <sup>2</sup> C interface by the external master.                                                                                                                                                                                                                                                                                         |

| MULTI BOOT                     | The derivative concept of MSPI, it refers to that FPGA reads bitstream data from different addresses of external Flash. The loading address of the latter bitstream data is written in previous bitstream data and the configuration is completed by triggering RECONFIG_N to switch the data stream file under the condition that the device power is on. FPGA products that support MSPI all support this mode. |

| Remote Upgrade                 | After an FPGA starts to work, if an upgrade is required, first write bitstream to an embedded or external Flash through remote operation, and then the FPGA reads the external Flash by triggering RECONFIG_N or powering up again to complete the configuration.                                                                                                                                                 |

| Daisy Chain                    | FPGA devices are connected sequentially in a serial way.  Devices can be configured from the head of the chain in sequence according to the connection order, and data can only be transmitted between adjacent devices.                                                                                                                                                                                          |

| User Mode                      | Hands over control to users when the FPGA configuration has been completed. Only in user mode, configuration pins can be reused as GPIOs (Gowin Programmable I/O).                                                                                                                                                                                                                                                |

| Edit Mode                      | FPGA can be programmed and configured in this mode. All configuration pins cannot be reused as GPIOs. The output of all GPIOs is high-impedance state, except transparent transmission.                                                                                                                                                                                                                           |

| ID CODE                        | Identification for the Gowin FPGA device. Each series of devices has a different number.                                                                                                                                                                                                                                                                                                                          |

| USER CODE                      | Used to identify the FPGA device that used. The user code can be written to the FPGA device through Gowin programmer. Up to 32-bit can be supported.                                                                                                                                                                                                                                                              |

| Security Bit                   | A special design for the configuration data security of Gowin FPGA product. After you write the bitstream with security bit to the device SRAM, no one will be able to read back the data. Gowin Software sets a security bit for the bitstream data of all FPGA products by default.                                                                                                                             |

| Encryption                     | Arora family of FPGA products supports this feature. After the encrypted bitstream is written to FPGA, the device will match the pre-stored key automatically, and then decrypt and wake up the device after successful matching. The device cannot work if matching fails.                                                                                                                                       |

UG290-2.6.7E 4(110)

# 3 Configuration Modes

## 3.1 LittleBee® Family of FPGA Products

Besides the JTAG configuration mode that is commonly used in the industry, the LittleBee® Family of FPGA products also support GOWINSEMI's own configuration mode: GowinCONFIG. GowinCONFIG configuration modes that are available and supported for each device depend on the device model and package. All non-volatile devices support JTAG and AUTO BOOT modes. Up to six configuration modes are supported, as shown in Table 3-1.

UG290-2.6.7E 5(110)

**Table 3-1 Configuration Modes**

| Configuration Modes |                                 | MODE[2:0] <sup>[1]</sup> | Description                                                                                                                |

|---------------------|---------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|

| JTAG                |                                 | XXX <sup>[2]</sup>       | The LittleBee® Family of FPGA products are configured via JTAG interface by external Host.                                 |

|                     | AUTO<br>BOOT                    | 000                      | FPGA reads data from embedded Flash for configuration                                                                      |

|                     | I <sup>2</sup> C <sup>[6]</sup> | 100                      | FPGA products are configured via I <sup>2</sup> C interface by external Host.                                              |

|                     | SSPI                            | 001                      | FPGA products of LittleBee® Family are configured via SPI interface.                                                       |

|                     | MSPI                            | 010                      | As a Master, FPGA reads data from an external Flash (or other devices) via the SPI interface <sup>[3].</sup>               |

| _                   | DUAL<br>BOOT <sup>[4]</sup>     | 110                      | FPGA reads data from external Flash first and if the external Flash configuration fails, it reads from the Internal Flash. |

|                     | SERIAL <sup>[5]</sup>           | 101                      | External Host configure FPGA products of LittleBee® Family via DIN interface.                                              |

|                     | CPU <sup>[5]</sup>              | 111                      | External Host configure FPGA products of LittleBee® Family via DBUS interface.                                             |

#### Note!

- [1] The unbound mode pins are grounded by default (except for GW1N(R)-2 and GW1N-1P5 devices, please refer to the corresponding pinout manuals).

- [2] The JTAG configuration mode is independent of MODE value.

- [3] The SPI interfaces of the SSPI and MSPI modes are independent of each other.

- [4] Currently GW1N(R)-4 / GW1N(R)-4B do not support DUAL BOOT.

- [5] The CPU configuration mode and SERIAL configuration mode share SCLK,

WE\_N and CLKHOLD\_N. The data bus pins for the CPU configuration mode share pins with MSPI and SSPI configuration modes.

- [6] Autoboot is automatically enabled in I<sup>2</sup>C mode. In I<sup>2</sup>C mode, following power-on the LittleBee devices will attempt to read data from the internal Flash first. The I<sup>2</sup>C SDA line MUST be held inactive (externally pulled-up) during Autoboot, otherwise the device maynot be configured correctly. Also, it is recommended to externally pull up the SCL line at the same time. Note that this note also applies to C version devices of which the SDA and SCL pins are with internal weak pull-up.

#### Note!

For details about configuration pins, pin reuse, and pin functions and application, please refer to <u>5 Configuration Pin</u>.

UG290-2.6.7E 6(110)

## 3.2 Arora Family of FPGA Products

Besides the JTAG configuration mode that is commonly used in the industry, the Arora Family of FPGA products also support GOWINSEMI's own configuration mode: GowinCONFIG. The GowinCONFIG configuration modes that are available and supported for each device depend on the device model and package. The Arora Family of FPGA Products support bitstream encryption and security bit setting, which provides safety for user designs. The Arora Family FPGA products support bitstream decompression; users can compress bitstream to save storage memory.

Table 3-2 lists the configuration modes that are supported by the Arora Family FPGA products.

| Table 3-2 | Configuration | Modes |

|-----------|---------------|-------|

|-----------|---------------|-------|

| Configuration Modes     |                     | MODE[2:0] <sup>1</sup> | Description                                                                                           |

|-------------------------|---------------------|------------------------|-------------------------------------------------------------------------------------------------------|

| JTAG                    | JTAG                |                        | External Host configures Arora Family of FPGA products via JTAG interface.                            |

| GowinCONFIG SERIAL CPU4 | MSPI                | 000                    | As Master, FPGA reads data from external Flash (or other devices) via the SPI interface <sup>3.</sup> |

|                         | SSPI                | 001                    | External Host configures Arora Family of FPGA products via SPI interface.                             |

|                         | SERIAL <sup>4</sup> | 101                    | External Host configures Arora Family of FPGA products via DIN interface.                             |

|                         | CPU <sup>4</sup>    | 111                    | External Host configures Arora Family of FPGA products via DBUS interface.                            |

#### Note!

- [1] The unbound mode pins are grounded by default.

- [2] The JTAG configuration mode is independent of MODE value.

- [3] The SPI interfaces of the SSPI and MSPI modes are independent of each other.

- [4] The CPU configuration mode and SERIAL configuration mode share SCLK, WE\_N and CLKHOLD\_N. The data bus pins for the CPU configuration mode share pins with MSPI and SSPI configuration modes.

#### Note!

For details about configuration pins, pin reuse, and pin functions and application, please refer to <u>5 Configuration Pin</u>.

UG290-2.6.7E 7(110)

# 4 Configuration Process

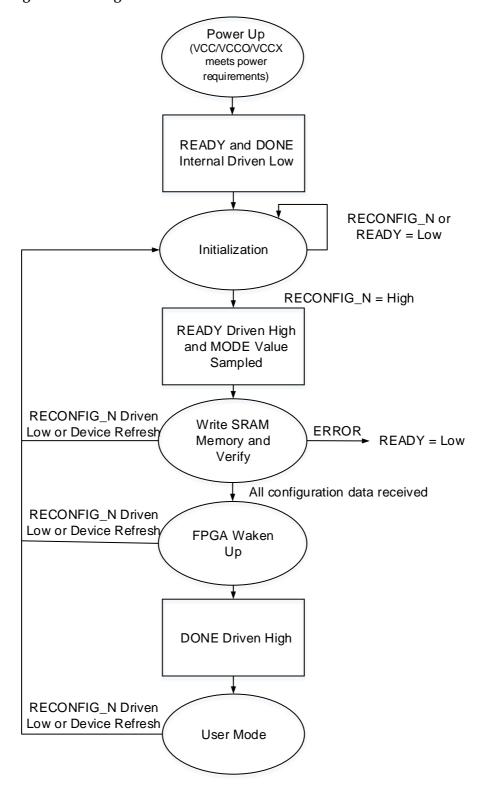

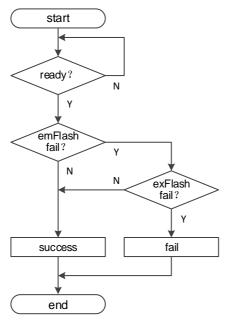

After power on, the FPGA goes through a sequence of states including initialization, SRAM configuration, and wake-up. The configuration flow is as shown in below.

UG290-2.6.7E 8(110)

**Figure 4-1 Configuration Flow**

UG290-2.6.7E 9(110)

## 4.1 Power-up Sequence

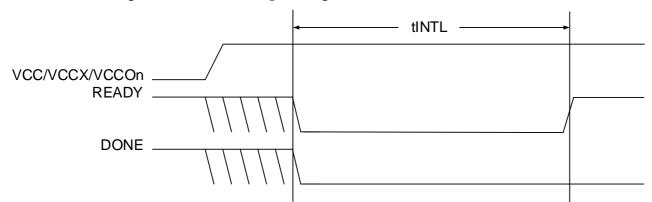

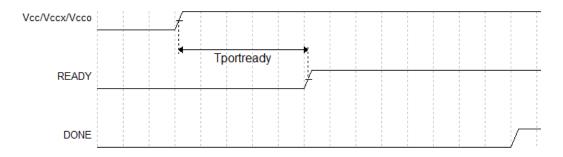

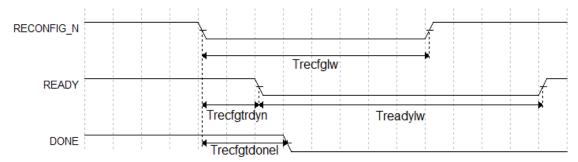

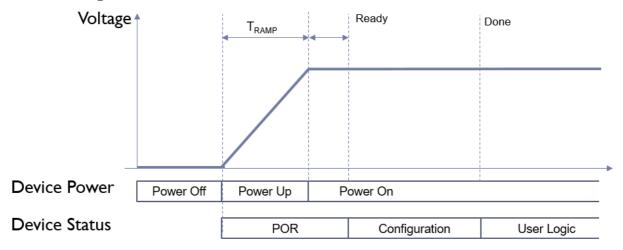

During the power-on process, the power-on reset (POR) circuit inside the FPGA becomes active. The actie POR circuit makes sure the external I/O pins are in a high-impedance state and monitors the VCC/VCCX/VCCOn input rails. When VCC/VCCX/VCCOn meets the minimum reset voltage level (Voltage level may vary for different devices, and different devices monitor different power rails.), POR circuit releases an internal reset signal, allowing the FPGA to bigin its initialization process. When READY and DONE are driven low, the FPGA moves to the initialization state, as shown in Figure 5-2.

Figure 4-2 POR Power-up Timing

Table 4-1 lists different power rails monitored by POR circuits of different devices.

| Series  | Device                                   | Power Rails          |

|---------|------------------------------------------|----------------------|

| GW1N    | GW1N-1<br>GW1N-4<br>GW1N-9               | VCC/VCCX/VCCO1/VCCO3 |

|         | GW1N-1P5<br>GW1N-2                       | VCC/VCCX/VCCO0       |

|         | GW1N-1S                                  | VCC/VCCX/VCCO0/VCCO2 |

| GW1NZ   | GW1NZ-1                                  | VCC/VCCX/VCCO1/VCCO3 |

| GW1NR   | GW1NR-1<br>GW1NR-2<br>GW1NR-4<br>GW1NR-9 | VCC/VCCX/VCCO1/VCCO3 |

| GW1NS   | GW1NS-4<br>GW1NS-4C                      | VCC/VCCX/VCCO0/VCCO1 |

| GW1NSR  | GW1NSR-4<br>GW1NSR-4C                    | VCC/VCCX/VCCO0/VCCO1 |

| GW1NSE  | GW1NSE-4C                                | VCC/VCCX/VCCO0/VCCO1 |

| GW1NSER | GW1NSER-4C                               | VCC/VCCX/VCCO0/VCCO1 |

| GW1NRF  | GW1NRF-4B                                | VCC/VCCX/VCCO1/VCCO3 |

| GW2A    | GW2A-18<br>GW2A-55                       | VCC/VCCX/VCCO3       |

| GW2AR   | GW2AR-18                                 | VCC/VCCX/VCCO3       |

| GW2AN   | GW2AN-9X                                 | VCC/VCCX/VCCO1/VCCO5 |

Table 4-1 Power Rails Monitored by POR Circuits of Different Devices

UG290-2.6.7E 10(110)

| Series | Device    | Power Rails    |

|--------|-----------|----------------|

|        | GW2AN-18X |                |

|        | GW2AN-55  | VCC/VCCX/VCCO3 |

| GW2ANR | GW2ANR-18 | VCC/VCCX/VCCO3 |

### 4.2 Initialization

After the power on reset circuit drives the READY and DONE status pins low, the FPGAs enter the memory initialization immediately. The purpose of the initialization is to clear all the SRAM memory inside the FPGA.

The FPGA remains in the initialization state until all of the following conditions are met:

- The T<sub>INITL</sub> time period has elapsed.

- The RECONFIG N pin is high.

- The READY pin is not driven low by an external driver.

The READY pin provides two functions during the initialization phase:

- To indicate that the FPGA is currently clearing its configuration SRAM

- To act as an input preventing the FPGA transition from the initialization state to the configuration state when it's driven low by an eternal driver.

## 4.3 Configuration

The rising edge of the READY pin causes the FPGA to enter the configuration state. The internal configuration SRAM of FPGA can be configured via multiple modes according to the MODE pin values. During the time the FPGA receives its configuration data, the READY pin can indicate its internal state. When READY is high, configuration proceeds without issue. If READY is low, an error has occurred and the FPGA does not operate.

### 4.4 Wake-up

When all the configuration data is reveived correctly, the FPGA enters the wake-up state and set the internal status bit of DONE to 1. In the wake-up state, the FPGA will perform the following operations in sequence:

- 1. Enable the Global output enable (GOE) signal, and then the FPGA I/O exits a high-impedance state and take on its programmed function. The input signals are prevented from performing any action on the FPGA flip-flops by the assertion of the Global Set/Reset (GSR).

- 2. Release the Global Set/Reset (GSR) signal and the Global Write Disable (GWDISn) signal. Enabling the Global Write Disable (GWDISn) signalp revents the FPGA from mistakenly overwriting the initialization data in the internal RAM.

- 3. Enable the external DONE pin. The external DONE is a bidirectional, open-drain I/O when it's enabled. Keep the FPGA wake-up by externally driving the DONE pin low. When the DONE pin is driven high, the FPGA wake-up pahse is complete and enters user mode.

UG290-2.6.7E 11(110)

4 Configuration Process 4.5 User Mode

### 4.5 User Mode

After entering user mode, the FPGA will perform the logic operations you designed immediately. The FPGA will remains in this state until one of the following three events occurs:

- The RECONFIG\_N pin is externally driven low.

- A REFRESH command is received via one of the configuration ports

- Power is cycled

Once one of the three envents above occurs, the FPGA will enter the configuration process again.

UG290-2.6.7E 12(110)

# 5 Configuration Pins

Gowin FPGA products have various configuration modes, including general JTAG configuration, active configuration, passive configuration, serial configuration and parallel configuration, etc., which can meet the various peripheral requirements of different users. The programming and configuration pins can be used as configuration pins and also can be reused as GPIO. Users can configure the pins as required. Users also can configure them according to their configuration functions to meet specific requirements.

## 5.1 Configuration Pin List and Reuse Options

### 5.1.1 Configuration Pin List

Table 5-1 contains a list of all the configuration pins of Gowin FPGA products together with the details of the pins used in each configuration mode and the shared pins in chip packages.

**Table 5-1 Configuration Pin List**

| Pin Name   | I/O | JTAG         | GowinCONFIG  |                  |              |              |              |              |              |

|------------|-----|--------------|--------------|------------------|--------------|--------------|--------------|--------------|--------------|

|            |     |              | AUTO<br>BOOT | I <sup>2</sup> C | SSPI         | MSPI         | DUAL<br>BOOT | SERIAL       | CPU          |

| RECONFIG_N | I   | √            | √            | <b>V</b>         | <b>√</b>     | √            | √            | √            | √            |

| JTAGSEL_N  | I   | $\checkmark$ |              |                  |              |              |              |              |              |

| TDO        | 0   | $\checkmark$ |              |                  |              |              |              |              |              |

| TMS        | I   | $\checkmark$ |              |                  |              |              |              |              |              |

| TCK        | I   | $\checkmark$ |              |                  |              |              |              |              |              |

| TDI        | I   | √            |              |                  |              |              |              |              |              |

| READY      | I/O | $\checkmark$ | $\checkmark$ | <b>V</b>         | $\checkmark$ | <b>√</b>     | √            | $\checkmark$ | $\checkmark$ |

| DONE       | I/O | √            | √            | <b>V</b>         | <b>V</b>     | √            | √            | √            | V            |

| MODE[2:0]  | ı   |              | $\sqrt{}$    | $\sqrt{}$        | $\checkmark$ | $\checkmark$ | $\sqrt{}$    | $\checkmark$ | $\checkmark$ |

| SCLK       | 1   |              |              |                  | √            |              |              | √            | √            |

UG290-2.6.7E 13(110)

| Pin Name      | I/O | JTAG | GowinCONFIG  |                  |          |              |              |        |              |

|---------------|-----|------|--------------|------------------|----------|--------------|--------------|--------|--------------|

|               |     |      | AUTO<br>BOOT | I <sup>2</sup> C | SSPI     | MSPI         | DUAL<br>BOOT | SERIAL | CPU          |

| CLKHOLD_N/DIN | 1   |      |              |                  | <b>√</b> |              |              | √      | √            |

| WE_N/DOUT     | 0   |      |              |                  |          |              |              | √      | √            |

| MI /D7        | I/O |      |              |                  |          | $\checkmark$ |              |        | $\checkmark$ |

| MO /D6        | I/O |      |              |                  |          | √            |              |        | √            |

| MCS_N /D5     | I/O |      |              |                  |          | √            |              |        | √            |

| MCLK /D4      | I/O |      |              |                  |          | √            |              |        | √            |

| FASTRD_N /D3  | I/O |      |              |                  |          | $\checkmark$ |              |        | $\checkmark$ |

| SI /D2        | I/O |      |              |                  | V        |              |              |        | √            |

| SO /D1        | I/O |      |              |                  | <b>V</b> |              |              |        | √            |

| SSPI_CS_N/D0  | I/O |      |              |                  | <b>V</b> |              |              |        | √            |

| SCL           | 1   |      |              | <b>√</b>         |          |              |              |        |              |

| SDA           | I/O |      |              | √                |          |              |              |        |              |

#### Note!

- For the configuration modes supported by different devices, please refer to 3Configuration Modes.

- Please refer to <u>6 Configuration Mode Introduction</u> for the definition of each pin in different configuration modes.

### **5.1.2 Configuration Pin Reuse**

To maximize the utilization of I/O, Gowin FPGA products support setting the configuration pins as GPIO pins. Before any configuration operation is performed on all series of Gowin FPGA products after power up, all related configuration pins are used as configuration pins by default. After successful configuration, the device enters into user mode and reassigns the pin functions according to the multiplex options selected by the user.

#### Note!

When setting the pin multiplexing option, ensure the external initial connection state of the pins does not affect the device configuration. Isolate the connections that affect the configuration first, and then wait to modify them in user mode.

The reuse options for the configuration pins are detailed in Table 5-2.

UG290-2.6.7E 14(110)

**Table 5-2 Pin Reuse Options**

| Name                  | Options        | Description                                                                                                                                                                                                    |  |  |

|-----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                       | Default Status | TMS, TCK, TDI, and TDO are used as dedicated configuration pins. JTAGSEL_N is used as GPIO.                                                                                                                    |  |  |

| JTAG PORT             | Set as GPIO    | JTAGSEL_N pins are used as dedicated configuration pins:  ■ JTAGSEL_N=0, TMS, TCK, TDI, and TDO are used as configuration pins:  ■ JTAGSEL_N = 1, TMS, TCK, TDI, and TDO are used as GPIO after configuration. |  |  |

| I <sup>2</sup> C PORT | Default Status | SCL and SDA pins are used as dedicated configuration pins.                                                                                                                                                     |  |  |

| I-C PORT              | Set as GPIO    | SCL and SDA pins are used as GPIO after configuration.                                                                                                                                                         |  |  |

| SSPI PORT             | Default Status | SCLK, CLKHOLD_N, SSPI_CS_N, SI and SO are used as dedicated configuration pins.                                                                                                                                |  |  |

|                       | Set as GPIO    | SCLK, CLKHOLD_N, SSPI_CS_N, SI and SO are used as GPIO after configuration.                                                                                                                                    |  |  |

| MSPI PORT             | Default Status | FASTRD_N, MCLK, MCS_N, MO and MI are used as dedicated configuration pins.                                                                                                                                     |  |  |

| WISPIPORI             | Set as GPIO    | FASTRD_N, MCLK, MCS_N, MO and MI are used as GPIO after configuration.                                                                                                                                         |  |  |

| RECONFIG N            | Default Status | Dedicated configuration pins.                                                                                                                                                                                  |  |  |

| RECONFIG_N            | Set as GPIO    | Used as GPIO after configuration.                                                                                                                                                                              |  |  |

| READY                 | Default Status | Dedicated configuration pins.                                                                                                                                                                                  |  |  |

|                       | Set as GPIO    | Used as GPIO after configuration.                                                                                                                                                                              |  |  |

| DONE                  | Default Status | Dedicated configuration pins.                                                                                                                                                                                  |  |  |

| DONE                  | Set as GPIO    | Used as GPIO after configuration.                                                                                                                                                                              |  |  |

#### Note!

- [1] For the devices with JTAGSEL\_N unbound, when debugging JTAG pin reuse, it's suggested to set MODE value to non-auto configuration mode (being neither autoboot, dual boot, nor MSPI) before power up to avoid the other bit stream data affecting configuration. Device turns into user MODE, and JTAG pin changes into GPIO after power up and manually configuring JTAG. After the device is power up, the device enters User Mode, and the JTAG pin is used as GPIO. For the LittleBee® Family of FPGA products, when MODE[2: 0]=001, the JTAGSEL\_N pin and the four JTAG Configuration pins (TCK, TMS, TDI, TDO) can be set as GPIOs simultaneously, but the JTAG pin cannot be recovered as a configuration pin by JTAGSEL\_N. It can be recovered when the device reenters the edit mode.

- [2] The pins of SERIAL and CPU modes are shared with other configuration modes, so they cannot be set as GPIOs separately. However, the pins can be set as GPIOs in non-shared configuration modes.

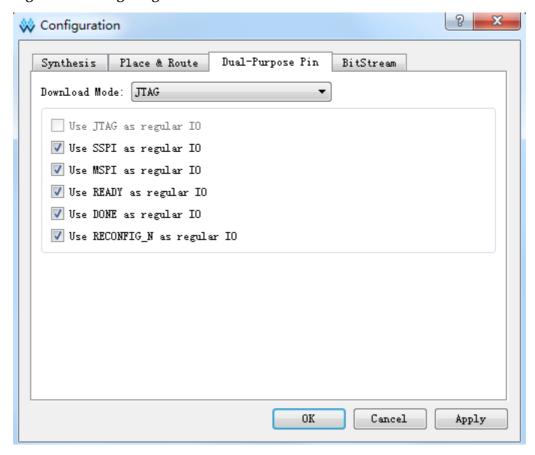

#### Configure Dual-purpose Pin

The steps are as follows:

- 1. Open the project in Gowin Software.

- 2. Select "Project > Configuration > Dual Purpose Pin" from the menu options, as shown in Figure 5-1.

UG290-2.6.7E 15(110)

Check the corresponding options.

Figure 5-1 Configuring Pin Reuse

## 5.2 Configuration Pin Function and Application

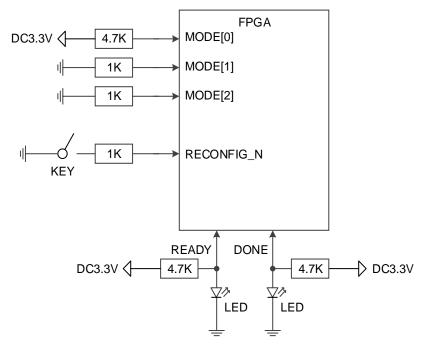

The RECONFIG\_N, READY, and DONE pins are used in all configuration modes. Other pins can be set as dedicated pins or GPIO (Gowin Programmable IO) according to their specific application.

**Table 5-3 Pin Function**

| Pin Name   | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RECONFIG_N | As a configuration pin, RECONFIG_N is an input pin that has an internal weak pull-up. Active low is used as the reset function for the FPGA programming configuration. FPGA can't be configured if RECONFIG_N is set to low. Keep high-level during FPGA powering up until the powering up is stable for 1ms.  As a configuration pin, a low level signal with pulse width no less than 25ns is required for GowinCONFIG to reload bitstream data according to the MODE setting value. You can also write logic to control the pin to trigger the device to reconfigure as required. As a GPIO pin, RECONFIG_N can only be used as the output pin. To ensure a smooth configuration, set the initial value of RECONFIG_N to high. |

| READY      | In-out pins. The default state is open-drain output with internal weak pull-up. Active-high. FPGA can be configured only when the READY signal is pulled up. When the READY signal is pulled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

UG290-2.6.7E 16(110)

| Pin Name   | Functional Description                                                                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------|

|            | down, recover the status by powering up or triggering                                                                      |

|            | RECONFIG_N.                                                                                                                |

|            | As an output configuration pin, it indicates that the FPGA can be                                                          |

|            | configured or not. If the FPGA meets the configuration condition,                                                          |

|            | the READY signal is high. If the configuration fails, READY signal                                                         |

|            | is low. As an input configuration pin, you can delay the                                                                   |

|            | configuration via its own logic or by pulling down the READY                                                               |

|            | signal.                                                                                                                    |

|            | As a GPIO, it can be used as an input or output type. If READY is                                                          |

|            | used as an input GPIO, the initial value needs to be 1 before                                                              |

|            | configuration. Otherwise, the FPGA cannot be configured. In-out pins. The default state is open-drain output with internal |

|            | weak pull-up, and DONE output 0 during configuration. A signal                                                             |

|            | which indicates FPGA is configured successfully, DONE is pulled                                                            |

|            | up after successfully configuring.                                                                                         |

|            | As an output configuration pin, it indicates the current                                                                   |

|            | configuration of FPGA: if configured successfully, the DONE signal                                                         |

|            | is high and the device enters into working state. if the                                                                   |

|            | configuration fails, the DONE signal keeps low. As an input                                                                |

| DONE       | configuration pin, the user can delay the entering of user mode via                                                        |

|            | its own internal logic or by reducing the DONE signal. When                                                                |

|            | RECONFIG_N or READY signals are low, DONE signal also                                                                      |

|            | keeps low. When configuring SRAM using JTAG circuit, it does not                                                           |

|            | need to take DONE signal into account.                                                                                     |

|            | As a GPIO, it can be used as an input or output type. <b>If DONE is</b>                                                    |

|            | used as an input GPIO, the initial value of DONE should be 1                                                               |

|            | before configuring. Otherwise, the FPGA will fail to enter the user mode after being configured.                           |

|            | GowinCONFIG modes selection pin. As the selection pin of                                                                   |

|            | GowinCONFIG modes, MODE is an input pin that has internal                                                                  |

|            | weak pull-up. The maximum bit width is 3 bits. When FPGA                                                                   |

|            | powers up or a low level pulse triggers RECONFIG N, the device                                                             |

|            | enters the corresponding GowinCONFIG mode in accordance with                                                               |

|            | the MODE value. The same MODE value of the different Gowin                                                                 |

|            | series of FPGA products may have different configuration MODE.                                                             |

| MODE       | As the number of pins for each package is different, some MODE                                                             |

|            | pins are not all bonded out, please refer to the corresponding                                                             |

|            | PINOUT manual for further details.                                                                                         |

|            | When MODE pins are used as GPIOs, they can be used as an                                                                   |

|            | input or output type.                                                                                                      |

|            | Note that when the MODE value changes, power-on again or providing one low pulse for triggering RECONFIG N is required     |

|            | for it to take effect.                                                                                                     |

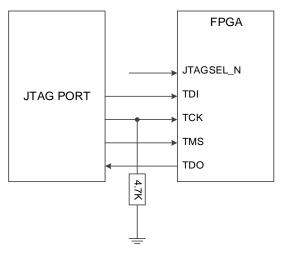

|            | As a configuration pin, it is an input pin with internal weak pull-up.                                                     |

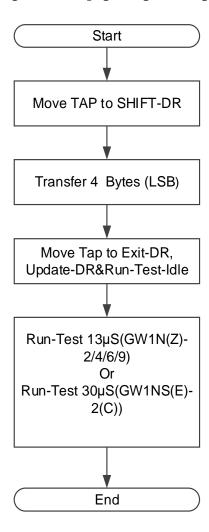

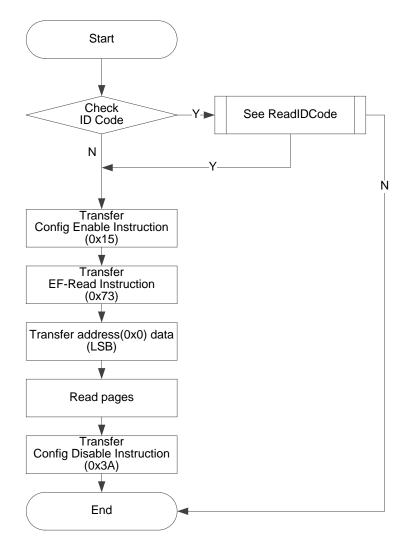

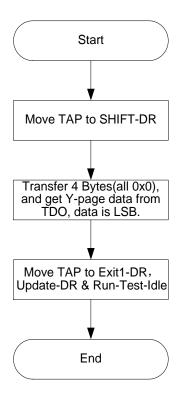

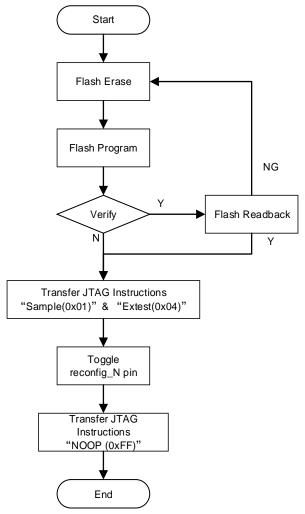

|            | If JTAG pins are set as a GPIO in the Gowin Software, the JTAG                                                             |